### 1.ЦИФРОВЫЕ ЭЛЕМЕНТЫ МИКРОПРОЦЕССОРНЫХ СИСТЕМ

### 1.1. Формы представления чисел.

В разные исторические периоды развития человечества для подсчётов и вычисления использовались те или иные системы счисления. Например, довольно широко была распространена двенадцатеричная система (дюжина, число месяцев в году). В древнем Вавилоне существовала шестнад- цатеричная система (1час=60мин.,1мин.=60с.)

У некоторых африканских племён была распространена пятеричная система счисления, у ацтеков и народов майя — двадцатеричная система. Десятичная система измерения возникла в Индии и затем завезена была арабами в Европу.

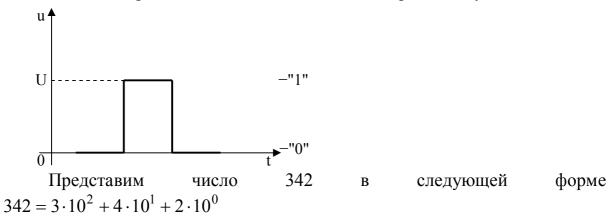

В технике, в ЭВМ и микропроцессорах широко используется двоичная система счисления, которая очень удобна в реализации для цифровых схем. Например, любой цифровой сигнал может иметь либо быть какое-то определенное значение, либо быть равным нулю:

Отсюда видно, что число 10 является основанием системы счисления, которая в данном случае называется десятичной, а величина числа определяется коэффициентами при основании.

Таким образом, в общем, виде числа можно представить в виде:

$$\dot{A} = \dot{a} \cdot \tilde{o}^{n} + b \cdot x^{n-1} + ... + p \cdot x^{1} + q \cdot x^{0}$$

В двоичной системе счисления основанием является число 2. В этом случае для записи чисел используются две цифры: 0 и 1. Возьмем, например число 12 в десятичной системе счисления и разложим его по степеням числа.

2. Получим:

$$12 = 1 \cdot 2^3 + 1 \cdot 2^2 + 0 \cdot 2^1 + 0 \cdot 2^0$$

Число 12 в двоичной системе счисления запишется следующим образом:  $1100_{(2)} = 12_{(10)}$

Перевод числа из десятичной системы счисления в двоичную производится методом последовательного деления числа на 2 до тех пор, пока частное от деления не станет равным 1. Число в двоичной системе счисления записывается в виде остатков от деления начиная с последнего частного справа налево:

$$\begin{array}{c|c|c}

-42 & 2 \\

42 & 21 & 2 \\

\hline

0 & 20 & 10 & 2 \\

\hline

1 & 10 & 5 & 2 \\

\hline

0 & 4 & 2 & 2 \\

\hline

1 & 2 & 1

\end{array}$$

$$42_{(10)} = 101010;$$

$$42_{(10)} = 1 \cdot 2^{5} + 0 \cdot 2^{4} + 1 \cdot 2^{3} + 0 \cdot 2^{2} + 1 \cdot 2^{1} + 0 \cdot 2^{0}$$

$$42_{(10)} = 1 \cdot 32 + 0 + 1 \cdot 8 + 2 + 0$$

Перевод десятичного дробного числа в двоичную систему осуществляется в два этапа: в начале переводится целая часть числа, затем дробная. Дробная часть переводится путём последовательного умножения дробной части на два. Двоичное число записывается в виде частей чисел, полученных при умножении только дробной части, начиная сверху после запятой. При этом задаётся точность выражений. Например, число 0,41(10) в десятичной системе преобразуется в число 0,011(2)

В микропроцессорных устройствах широко распространены и другие системы счисления: восьмеричная, шестнадцатеричная, двоично-десятичная:

| десятичная | двоичная | восьмеричная | шестнадцати-<br>ричная | двоично-десятичная |

|------------|----------|--------------|------------------------|--------------------|

| 0          | 0        | 0            | 0                      | 0000               |

| 1          | 1        | 1            | 1                      | 0001               |

| 2          | 10       | 2            | 2                      | 0010               |

| 3          | 11       | 3            | 3                      | 0011               |

| 4          | 100      | 4            | 4                      | 0100               |

| 5          | 101      | 5            | 5                      | 0101               |

| 6          | 110      | 6            | 6                      | 0110               |

| 7          | 111      | 7            | 7                      | 0111               |

| 8          | 1000     | 10           | 8                      | 1000               |

| 9          | 1001     | 11           | 9                      | 1001               |

| 10         | 1010     | 12           | Α                      | 0001 0000          |

| 11         | 1011     | 13           | В                      | 0001 0001          |

| 12         | 1100     | 14           | С                      | 0001 0010          |

| 13         | 1101     | 15           | D                      | 0001 0011          |

| 14         | 1110     | 16           | Е                      | 0001 0100          |

| 1: | 5 | 1111  | 17 | F  | 0001 | 0101 |

|----|---|-------|----|----|------|------|

| 10 | 6 | 10000 | 20 | 10 | 0001 | 0110 |

| 1  | 7 | 10001 | 21 | 11 | 0001 | 0111 |

| 1  | 3 | 10010 | 22 | 12 | 0001 | 1000 |

| 1  | 9 | 10011 | 23 | 13 | 0001 | 1001 |

| 2  | ) | 10100 | 24 | 14 | 0010 | 0000 |

Сложением чисел в двоичной системе счисления осуществляется поразрядно начиная с младшего:

$$\frac{+\frac{7}{5}}{12} \qquad \frac{111}{0101} \quad -\text{перенос} \\

\frac{+0111}{0101} \\

1100$$

Операция вычитания в МП осуществляется так же, как и сложение, но при этом отрицательные числа представляются в дополнительном или обратном коде.

Дополнительный код отрицательных двоичных чисел получается заменой двоичных кодов во всех разрядах на взаимно-обратные (0 на 1, 1 на 0). После этого к младшему разряду добавляется 1. В знаковом разряде отрицательного числа записывается 1.

Например:

$$[-14]_{\text{доп}} = [-0.1110]_{\text{доп}} = [1.0001+1] = 0,0010$$

При записи чисел в обратном коде в знаковом разряде записывается 1, а в остальных разрядах цифры заменяются на взаимообратные: Например:  $[-14]_{\text{обр.}}=[-0,1110]_{\text{обр.}}=1,0001$ .

При выполнении операции вычитания производится поразрядное сложение слагаемых, начиная с младшего и кончая знаковым разрядом. Если используется дополнительный код, то возможная единица переноса из знакового разряда отбрасывается, при использовании обратного кода единица переноса знакового разряда суммируется с младшим разрядом полученной суммы. Результат вычислений получается в том коде, в каком были предоставлены слагаемые.

При сложении чисел, представленных в двоично-десятичном коде, суммирование осуществляется потетрадно, формируя двоичный код соответствующего двоичного разряда. Если сумма результата в тетраде превышает 9, к нему прибавляется двоичный код  $0110_{(2)}$  числа  $6_{(10)}$ .

При этом в старшем разряде тетрады возникает единица переноса, соответствующая десятичному числу 16, которая равносильна вычитанию

16 из данной тетрады.

Таким образом, при результате, превышающем 9, в тетраде будет записано число, уменьшенное на 16-6=10, что и требуется для формирования двоично-десятичного числа. Например:

Операции сложения и вычитания являются основными операциями в МП. Это объясняется тем, что они легко выполняются и любые более сложные операции (умножение, деление, вычисление тригонометрических функций и т.д.) могут быть сведены многократным сложениям и вычитаниям.

### 1.2. Комбинационные логические схемы.

Все устройства в МП состоят из элементарных логических схем. Работа этих схем основана на законах и правилах алгебры логики, которая оперирует двумя понятиями: истинности и ложности высказывания. В соответствии с такой двоичной природой высказываний условились называть их логическими двоичными переменными и обозначать 1 в случае истинности и 0 в случае ложности. Преобразование связей между логическими переменными осуществляется в соответствии с правилами алгебры логики, называемой алгеброй Буля или Булевой алгеброй (в честь её автора - английского математика Буля Джоржа).

Две логические переменные  $\mathbf{A}$  и  $\mathbf{B}$ , принимающие значение 0 или 1, могут образовывать логические функции. Всего существует 16 возможных функций.

1) Логическое отрицание HE переменной A есть логическая функция X, которая истина только тогда, когда ложно A и наоборот.

В алгебре логики любые функции удобно изображать в виде таблицы соответствия всех возможных комбинаций входных логических переменных и выходной логической функции, называемой таблицей истинности. Для функции логического отрицания *НЕ* таблица истинности имеет вид:

| A | 0 | 1 |  |

|---|---|---|--|

| X | 1 | 0 |  |

где A - входная переменная, X - выходная функция.

Функция НЕ в символах алгебры логики записывают следующим образом:  $X = \overline{A}$

Графически эта функция обозначается кружком на входе или выходе логического символа:

$$A \qquad X = \overline{A}$$

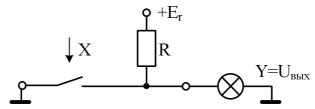

Практически эта функция реализуется переключателем, у которого замкнутое состояние соответствует «1», а разомкнутое - «0».

Временная диаграмма функции НЕ имеет вид:

2) Логическое умножение  $\boldsymbol{U}$  или конъюнкция двух переменных  $\boldsymbol{A}$  и  $\boldsymbol{B}$  есть логическая функция  $\boldsymbol{X}$ , которая истинна только тогда, когда одновременно истинны входные переменные.

Для функции логического умножения таблица истинности имеет вид:

| A | 0 | 0 | 1 | 1 |

|---|---|---|---|---|

| В | 0 | 1 | 0 | 1 |

| X | 0 | 0 | 0 | 1 |

и записывается как  $X = A \cdot B$   $X = A \wedge B$

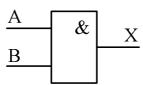

Графически функция И обозначается в виде прямоугольника

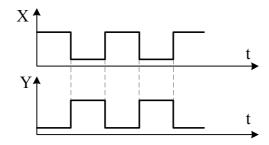

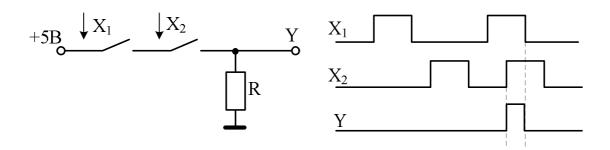

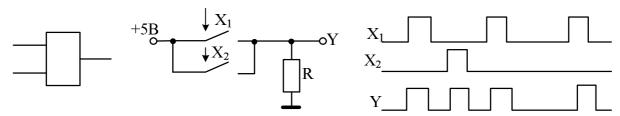

Практический размер реализации функции  $\emph{\textbf{\textit{U}}}$  и её временные диаграммы имеет вид:

| A | 0 | 0 | 1 | 1 |

|---|---|---|---|---|

| В | 0 | 1 | 0 | 0 |

| X | 1 | 1 | 1 | 0 |

3) Логическая сумма UJU или дизьюнкция переменных A и B есть логическая функция X, которая истинна, когда хотя бы одна из входных функций истинна. Для логической суммы таблица истинности имеет вид:

| A | 0 | 0 | 1 | 1 |

|---|---|---|---|---|

| В | 0 | 1 | 0 | 1 |

| X | 0 | 1 | 1 | 1 |

и записывается так:  $X = A + B = A \vee B$

Пример функции логической суммы двух переменных и диаграммы входных и выходных сигналов представлены на рис:

Широкое распрстранение получили в реализации современных логических схем функции *ИЛИ-НЕ*, *И-НЕ*, исключающее *ИЛИ*. Таблицы истинности этих схем имеют вид:

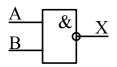

4) Функция И-НЕ (Отрицание коньюнкции или стрелка Пирса)

$$X = \overline{A \cdot B}$$

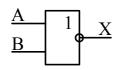

5) Функция ИЛИ-НЕ (Отрицание дизъюнкции или Штрих Шеффер)

| A | 0 | 0 | 1 | 1 |

|---|---|---|---|---|

| В | 0 | 1 | 0 | 1 |

| X | 1 | 0 | 0 | 0 |

$$X = \overline{A \vee B}$$

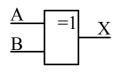

6) Функция исключающая ИЛИ (Неравнозначность или сложении по модулю 2)

$$X = A \oplus B$$

| A | 0 | 0 | 1 | 1 |

|---|---|---|---|---|

| В | 0 | 1 | 0 | 1 |

| X | 0 | 1 | 1 | 0 |

Кроме перечисленных функций в алгебре логики имеются следующие теоремы:

- 1.  $\mathbf{x} \vee \mathbf{0} = \mathbf{x}$

- 2.  $x \lor 1 = 1$

- 3.  $x \lor x \lor x \lor ... \lor x = x$

- 4.  $x \vee x = 1$

- 5.  $x \cdot 0 = 0$

- 6.  $x \cdot 1 = x$

- 7.  $\mathbf{x} \cdot \mathbf{x} \cdot \mathbf{x} \cdot \dots \cdot \mathbf{x} = \mathbf{x}$

- 8.  $\mathbf{x} \cdot \mathbf{x} = 0$

- 9.  $\bar{x} = x$

- 10. a)  $x \lor y = y \lor x$  Переместительный

- б)  $x \cdot y = y \cdot x$  закон

- 11. a)  $x \lor y \lor z = x \lor (y \lor z) = (x \lor y) \lor z$  Сочетательный

- б) xyz = x(yz) = (xy)z

закон

- 12.  $x(y \lor z) = xy \lor xz$  Распределительный закон

- 13.  $\overline{x \lor y} = \overline{x} \cdot \overline{y};$   $\overline{x \lor y \lor z} = \overline{x} \cdot \overline{y} \cdot \overline{z}$  $\overline{xy} = \overline{x} \lor \overline{y};$   $\overline{xyz} = \overline{x} \lor \overline{y} \lor \overline{z}$

Теоремы де-Моргана

Технический аналог булевой функции – комбинационная схема, выполняющая соответствующее этой функции преобразование информации.

### 1.3. Схемотехника цифровых логических элементов.

В микропроцессорной схемотехнике установлены следующее основные понятия и термины.

<u>Интегральная микросхема</u> (ИМС). Называется микроэлектронное изделие, выполняющее определенную функцию преобразования и имеющая большую плотность упаковки электрически соединенных элементов.

<u>Корпус ИМС</u> — часть конструкции ИМС, предназначенное для защиты ИМС от внешних воздействий и для соединения с внешними целями посредством выводов. В одном корпусе ИМС может находиться несколько ЛЭ, поэтому иногда принято характеризовать сложность той или иной схемы числом корпусов.

<u>Степень интеграции ИМС</u> – показатель степени сложности ИМС, характеризуемый числом содержащихся в ней элементов и компонентов. Существуют ИМС малой (МИС), средней (СИС) и большой (БИС) степени интеграции.

<u>Серия ИМС</u> – совокупность типов ИМС, которые могут выполнять различные функции, имеет единое конструктивно-технологическое исполнение и предназначены для совместного применения.

Используемые в МП устройствах ИМС характеризуется большим количеством показателей, которые определяют их функциональные возможности, быстродействие, экономичность, надежность, условия эксплуатации, стоимость и параметры входных и выходных сигналов.

По схемно-технологической реализации ИМС делят на следующие виды:

ЭСЛ-эмиттерно-связанные транзисторные схемы;

ТТЛ – транзисторно-транзисторные схемы;

${\rm H}^2{\rm \Pi}$  – интегральные инжекционные схемы;

ТТЛЩ – ТТЛ с диодами Шотки;

рМОП и nМОП схемы на p- и n- канальных транзисторах со структурой металл-окисел-полупроводник;

${\rm KMO\Pi}$  – схемы на дополняющих (комплементарных)  ${\rm MO\Pi}$  транзисторах.

По выполняемым функциям ИМС делят на комбинационные, запоминающие и содержащие как комбинационные, так и запоминающие схемы.

Потребляемая мощность и быстродействие ИМС зависят от режима работы (статический 0 и 1 на выходе, переключение из 1 в 0 или из 0 в 1), параметров нагрузки и других факторов. В большинстве случаев под потребляемой мощностью понимается ее среднее значение. Аналогично для оценки скоростных свойств ИМС используют среднее время задержки распространения сигнала при включении и выключении ИМС.

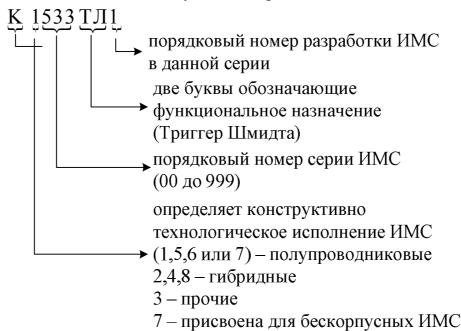

Обозначаются ИМС следующим образом:

На сегодняшний день широкое распространение получили следующие серии ИМС:

155, 176, 530, 531, 555 – ИМС с МИС и СИС 580, 581, 588, 1801, 1810 – ИМС с БИС и МП наборы.

# 1.4. Триггеры

**Триггером** (типичная схема цифрового автомата) называется устройство с двумя устойчивыми состояниями, содержащий элемент памяти(собственно Триггер) и схему управления, выполненную, как правило с помощью комбинации схем.

# Классификация триггеров

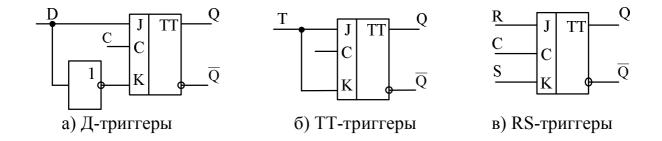

- 1. Различают четыре триггерные схемы типа D,T,SR и JK

- 2. По уровню входного сигнала триггеры разделяют на триггеры с прямыми входами (запись информации осуществляется уровнем «1») и с инверсными входами (запись производиться уровнем «0»), в последнем

случае вход отличается знаком инверсии.

- 3. Кроме того, триггеры бывают однотактные и двухтактные. В однотактных триггерах запись производится по переднему фронту сигнала записи, а в двукратных по заднему фронту, т.е. в момент окончания сигнала.

- 4. Все триггеры, в свою очередь делятся на синхронные и асинхронные. В синхронных триггерах информация записывается только при наличии синхросигнала, а в асинхронных в любой момент времени.

Рассмотрим более подробно работу каждой триггерной схемы:

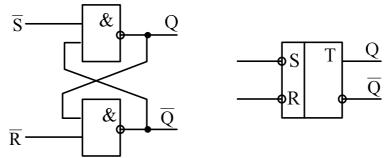

### RS-триггер

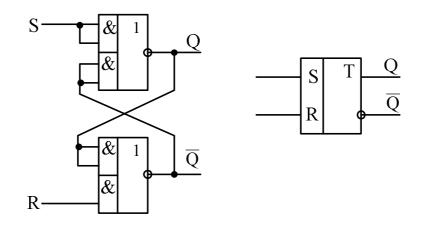

RS-триггер имеет следующие графические изображения:

Асинхронный RS – триггер с инверсными входами

Асинхронный RS – триггер с прямыми входами

Таблица истинности для RS - триггера

| Татичта  | Входы |     |     |     |

|----------|-------|-----|-----|-----|

| Текущие  | S=0   | S=0 | S=1 | S=1 |

| значения | R=0   | R=1 | R=0 | R=1 |

| Q=0      | 0     | 0   | 1   | X   |

| Q=1      | 1     | 0   | 1   | X   |

Таким образом RS - триггером называется логическое устройство с двумя устойчивыми состояниями и двумя информационными входами R и S. При подаче сигнала записи по входу S в триггер записывается «1» т.е.  $Q=1, \overline{Q}=0$ .При подаче сигнала записи по входу R в триггер записывается «0», т.е.  $Q=0, \overline{Q}=1$ . Одновременная подача сигналов в записи на входы – запрещенная комбинация, т.к. после окончания их действия триггер устанавливается в неопределенное состояние.

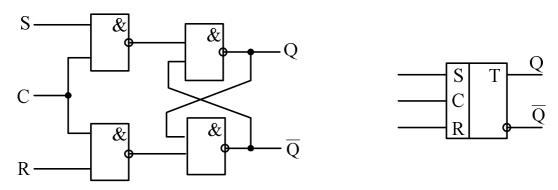

В отличии от асинхронного синхронный триггер на каждом информационном входе имеет дополнительные схемы совпадения, первые входы которых объединены и на них подаются синхронизирующие сигналы. Вторые входы схем сравнения являются информационными.

Наличие схем совпадения приводит к тому, что триггер будет срабатывать от сигналов R и S только при наличии синхросигнала, т.е. когда C=«1», при C= «0» входы R и S закрыты и состояние триггера не изменяется.

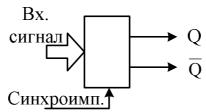

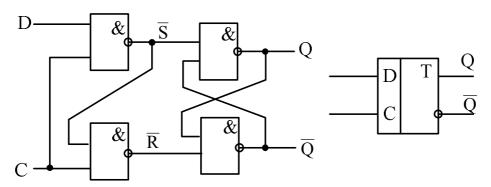

<u>D</u> – <u>триггер</u> имеет только один входной сигнал и его состояние определяется этим сигналом, т.е. триггер приводится в состояние сброса, когда входной сигнал имеет высокий уровень.

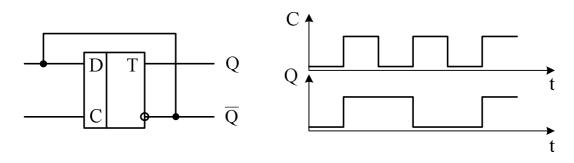

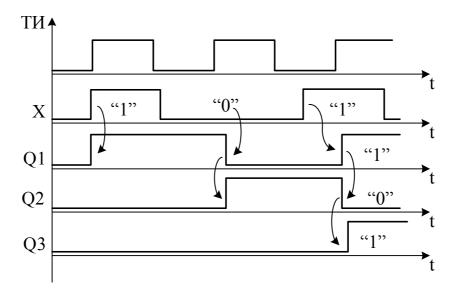

В литературе такой триггер называется триггером задержки. Интересно применение такого триггера в качестве делителя частоты. Схема и диаграмма работы имеют следующий вид:

| Текущее   | Входы |     |  |

|-----------|-------|-----|--|

| состояние | D=0   | D=1 |  |

| Q=0       | 0     | 1   |  |

| Q=1       | 0     | 1   |  |

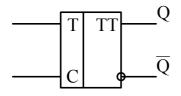

Триггером Т-типа (счётный триггер) называется логическое устройство (с двумя устойчивыми состояниями и одним входом Т), изменяющее своё состояние на противоположное всякий раз когда на вход Т поступает управляющий сигнал.

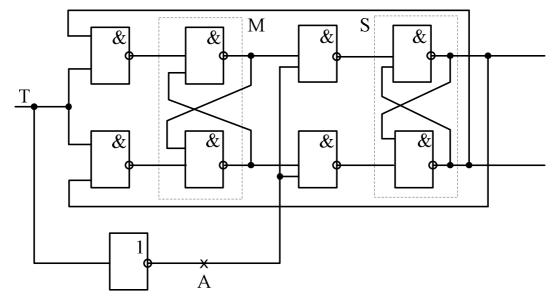

Схема и условное графическое изображение имеют вид:

а) Схема

| Текущее   | Входы |     |  |

|-----------|-------|-----|--|

| состояние | T=0   | T=1 |  |

| Q=0       | 0     | 1   |  |

| Q=1       | 1     | 0   |  |

б) Условное изображение

в) Таблица состояний

Основной триггер М принимает информацию, а вспомогательный S, фиксирует состояние триггера со счетным входом. Инвертор на схеме обеспечивает однотактный режим работы триггера М и осуществляет блокировку записи информации во вспомогательный триггер S одновременно с записью информации в основной триггер М.

Если исключить инвертор и в точку А подать другую серию тактовых импульсов, сдвинутую относительно серии, действующей на входе Т, то получим двухтактный ТТ-триггер. При действии сигнала на вход Т информация записывается в основной триггер М, а затем при действии сигнала на вход А информация переписывается во вспомогательный триггер S.

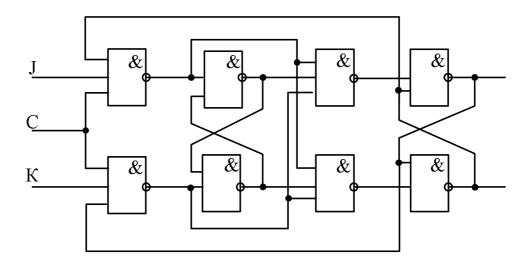

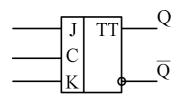

<u>JK-триггер</u> аналогичен RS триггеру, за исключением того, что когда на оба входа подаются сигналы высокого уровня, триггер изменяет своё состояние независимо от своего текущего состояния, т.е. JK-триггер в отличии от RS-триггера не имеет запрещенных состояний.

Схема синхронного ЈК-триггера.

Условные обозначение.

Таблица состояний.

| Текущее   | Входы      |     |     |     |  |

|-----------|------------|-----|-----|-----|--|

| состояние | J=0<br>K=0 | J=0 | J=1 | J=1 |  |

| ОСТОЯНИС  | K=0        | K=1 | K=0 | K=1 |  |

| Q=0       | 0          | 0   | 1   | 1   |  |

| Q=1       | 1          | 0   | 1   | 0   |  |

JK-триггер является универсальным логическим элементом, получившем очень широкое практическое применение. На базе этого триггера можно реализовать любой раннее рассмотренный триггер:

### 1.5. Регистры

Регистром называется узел цифровых схем МП устройств, предназначенный для приёма, хранения и выдачи кодов слов, а так же выполняющий некоторые логические преобразования над кодом числа. Регистр представляет собой совокупность триггеров и вспомогательных логических элементов, количество и схема соединений которых зависит от числа разрядов в коде набора операций, выполняемых регистром.

Помимо хранения кода слов регистры обеспечивают выполнение следующих операций:

- 1) установку регистра в нулевое состояние (сброс);

- 2) передачу кода слова в другое устройство;

- 3) приём кода слова из другого устройства;

- 4) преобразование прямого кода в обратный и наоборот;

- 5) преобразование последовательного кода слова в параллельный и наоборот;

- 6) сдвиг кода слова вправо или влево на требуемое число разрядов.

Регистры, как правило строятся на D триггерах, так как последние позволяют записывать информацию однофазным кодом по входу D без предварительного обнуления.

Приём информации в регистр и её выдача могут осуществляться параллельно и последовательно. В первом случае слово представляется в виде параллельного кода, т.е. при записи и считывания все разряды кода слова представляются одновременно, каждый разряд по своей кодовой шине.

При последовательной передаче кода слова все его разряды передаются последовательно во времени один за другим и строго в определенные дискретные моменты времени, совпадающие с управляющими сигналами.

<u>Классификация.</u> В соответствии с выполняемыми функциями регистры различаются на сдвигающие регистры и регистры без сдвига с приёмом информации параллельным кодом.

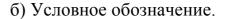

<u>Регистр с приёмом информации параллельным кодом.</u> Эти регистры предназначены для приёма, хранения и выдачи кода одного n-раздельного

слова. Т.к. приём и выдача информации осуществляется в параллельном коде, рассматриваемый п-разрядный регистр сложно представить как совокупность одноразрядных регистров, имеющих общие шины управления. Примером такого регистра служат ИМС серий 580 и 1810 - K580 и P82,83,K1810 и P82,83.

а) Структурная схема К580UP82.

Микросхема имеет 8 триггеров D-типа и восемь выходных буферов имеющих на выходе состояние «Выключено». При поступлении сигнала высокого уровня осуществляется нетактируемая передача информации от входа  $D_i$  до выхода  $Q_i$ . Выходные буферы управляются сигналом OE «Разрешение выхода». При поступлении на вход OE сигнала высокого уровня выходные буферы переводят в состояние «Выключено».

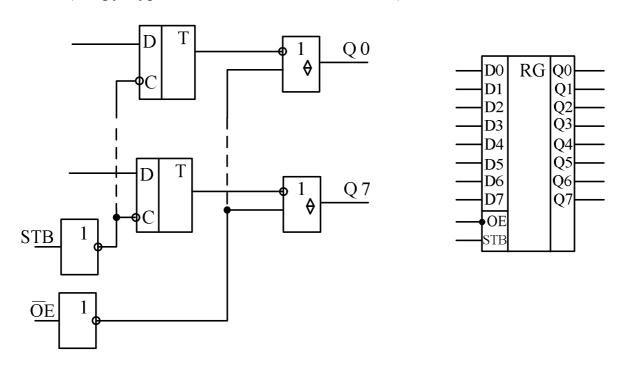

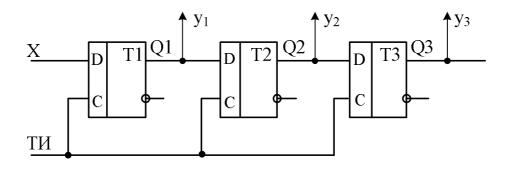

Сдвигающие регистры. В регистрах этого типа, выполненных на D-триггерах, осуществляется сдвиг слова влево или вправо на заданное число разрядов — за один такт на один разряд. Применяют эти регистры в основном для преобразования параллельного кода в последовательный и наоборот, а так же в арифметических устройствах при операциях под специальными кодами.

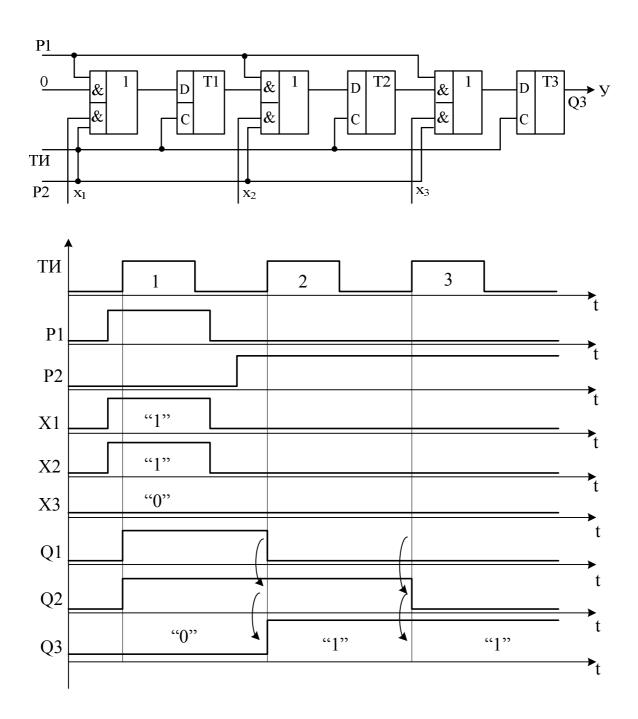

Рассмотрим сдвигающий регистр, выполняющего операцию преобразования последовательного кода в параллельный.

Входное слово для данного примера  $X_1X_2X_3=X=101$  в последовательном коде поступает на вход D-триггера T1 старшим разрядом вперёд.

Схема сдвигающего регистра.

Временная диаграмма

При поступлении первого ТИ код  $X_3$  переписывается в Т1, второй ТИ переписывает  $X_3$  в Т2, а в Т1 записывает  $X_2$ , третий ТИ код  $X_3$  переписывается в Т3, код  $X_2$  переписывается в Т2, а в Т1 записывают  $X_1$ . Таким образом, после трёх тактирующих импульсов всё число окажется записанным в регистр и может быть считано в параллельном коде с выходом  $Q_1, Q_2, Q_3$ .

Рассмотрим сдвигающий регистр для преобразования параллельного кода в последовательный. Входное слово (для данного примера)  $X=X_1X_2X_3=011$  при  $P_1 \wedge [TH]=1$  и  $P_2=0$  записывается в T1,T2,T3. Затем при  $P_2 \wedge [TH]=1$  и  $P_1=0$  происходит перезапись информации из T1 в T2, из T2 в T3 и т.д. из младшего разряда в старший по каждому тактирующему импульсу. Таким образом, на выходе последнего разряда  $Q_3$  будут последовательно появляться  $X_1X_2X_3$ , т.е. входное слово X, представленное в параллельном коде, преобразуется в выходное слово  $Y=y_3y_2y_1=011$ , представленное в последовательном коде.

В представленных схемах количество регистров зависит от разрядности преобразуемого слова.

### 1.6.Счетчики

Наиболее распространенной, операцией в вычислительных устройствах цифровой обработки информации, является подсчёт числа сигналов импульсного или потенциального вида. Узел вычислительных устройств, предназначенный для подсчёта числа входных сигналов, называется счетчиком.

Счетчики классифицируются:

- 1) по системе счисления: двоичные и десятичные;

- 2) по организации цепей переноса: счетчики с последовательным и параллельным переносом единицы;

- 3) по реализуемой операции: счетчики с естественным и произвольным порядком счета;

- 4) по порядку изменения состояний: прямые и реверсивные;

- 5) по способу переключения триггеров: асинхронные и синхронные.

Рассмотрим наиболее распространенные типы счетчиков.

<u>Счетчики с естественным порядком счёта.</u> Счетчики этого типа в основном строятся на универсальных JK и D-триггерах.

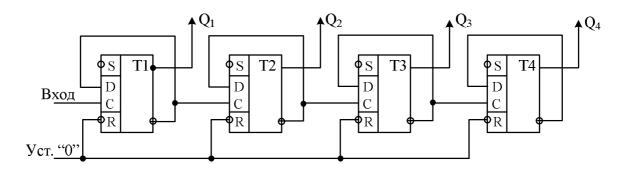

Простейшая схема счетчика последовательно соединенные D-триггеров со счетным входом. При этом инверсный выход  $\overline{Q}$  D-триггера соединяют со своим входом D.

Суммирующий асинхронный счетчик на  $\overline{Q}$  - Соединить со входом  $\overline{Q}$  последующего триггера. При этом схема асинхронного четырех разрядного суммирующего счетчика на  $\overline{D}$ -триггерах имеет следующий вид:

Для построения вычитающего счетчика на D-триггерах прямой выход предыдущего счетчика соединяют со входом C последующего триггера.

Рассмотренные счетчики обладают низким быстродействием и называются счетчиками с последовательным переносом единицы. Время установления таких счетчиков равно сумме времен установления всех триггеров. Увеличение быстродействия можно достигнуть путём уменьшения времени распространения переноса, используя счетчики с параллельным переносом единицы. При этом входной сигнал поступает одновременно на все входы триггеров.

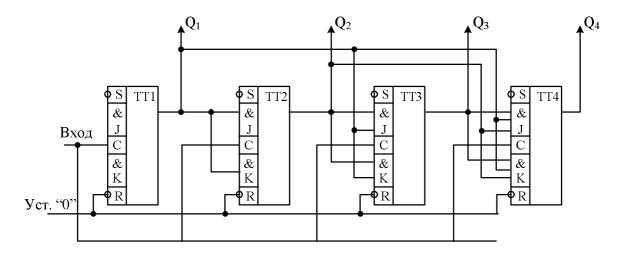

Схема синхронного счетчика на ЈК – триггерах с параллельным переносом единицы имеет следующий вид:

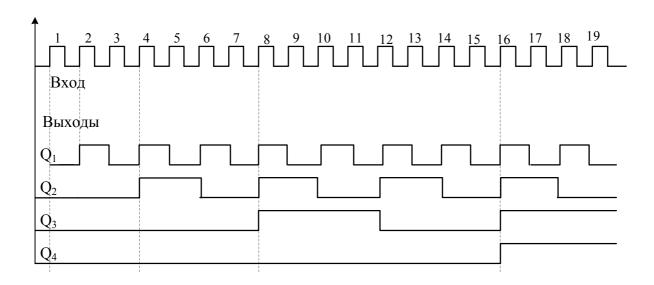

Работа счетчика осуществляется следующим образом. Каждый ЈКтриггер включен по схеме триггера D-типа, работающего в режиме делителя частоты на 2. На каждый второй импульс на выходе  $Q_1$  появляется импульс; который подаётся на вход D последующего триггера и на выходы совпадения триггеров TT3 и TT4. На каждый четвертый импульс появляется импульс на выходе  $Q_2$ , который подается на выходы сравнения TT3 и TT4. На каждый восьмой тактовый импульс появляется импульс на выходе TT3, который подается на схему сравнения TT4. При этом длительность импульсов триггеров равна соответственно TT40. Ири длительностям тактового импульса. Временная диаграмма такого счетчика выглядит следующим образом:

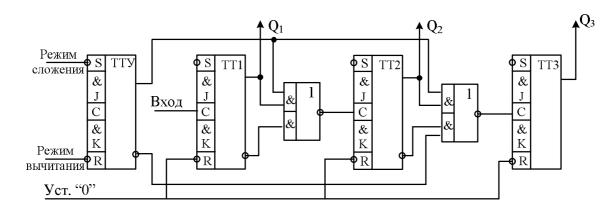

Большое распространение получили реверсивные счетчики, осуществляющие подсчет сигналов как в прямом, так и обратном направлении, т.е. они могут работать в режиме сложения или вычитания сигналов, поступающих на вход счетчика.

Для построения реверсивных счетчиков необходимо предусмотреть

схемы, пропускающие сигналы на вход следующих триггеров либо с прямого либо с инверсного выхода предыдущего триггера. Пример такого счетчика, построенного на ЈК – триггерах приведена ниже:

Триггер управления ТТУ формирует на выходах Q и  $\overline{Q}$  сигналы "0"или"1" и "1"или"0" в зависимости от установки триггера либо по вход  $\overline{Q}$

$\overline{S}$  или по входу  $\overline{R}$  согласно таблице истинности для этого триггера. Эти сигналы управляют дополнительными элементами  $\boldsymbol{U}-\boldsymbol{U}\boldsymbol{J}\boldsymbol{U}-\boldsymbol{H}\boldsymbol{E}$ , пропускающими сигналы от прямых или инверсных выходов и счетных триггеров TT1,TT2 и TT3.

Рассмотренные выше счетчики имели коэффициент пересчета, равный  $2^n$ , где n-число разрядов счетчика. Однако на практике часто возникает необходимость в счетчиках, коэффициент пересчета которых отличен от  $2^n$ . Такие счетчики являются с произвольным порядком счета.

Счетчики с произвольным порядком счета. На основе таких счетчиков можно построить пересчетные схемы с произвольным коэффициентом счета. Существует целый ряд схемных решений позволяющих построить счетчик с  $K_{cr} \neq 2^n$ . Наибольшее распространение получили счетчики с коэффициентом деления 10.

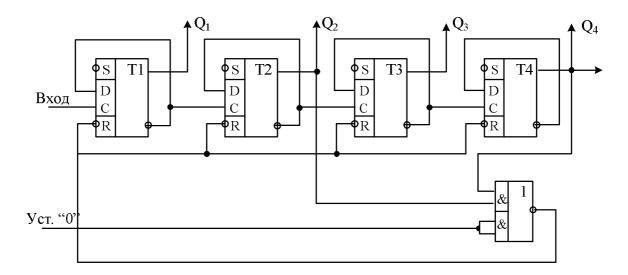

Рассмотрим схему десятичного счетчика на основе D – триггеров.

У такого счетчика уменьшение числа устойчивых состояний достигается за счет сбрасывания его в нулевое состояние при записи заданного числа сигналов. К счетчику добавляется логическое устройство, которое вырабатывает сигнал сброса счетчика в нулевое состояния при достижении состояния счетчика 1010, т.е. соответствующее числу 10.

## 1.7.Дешифраторы

Дешифратором называется цифровое комбинационное устройство, предназначенное для преобразования входного двоичного кода в напряжение логического уровня, появляющееся в том выходном проводе, десятитысячный номер которого соответствует двоичному коду. Например, входной код 1001 должен сделать активным провод с номером 9. Во всех остальных проводах дешифратора сигналы должны быть нулевыми.

Различают дешифраторы с линейной и координатной выборкой.

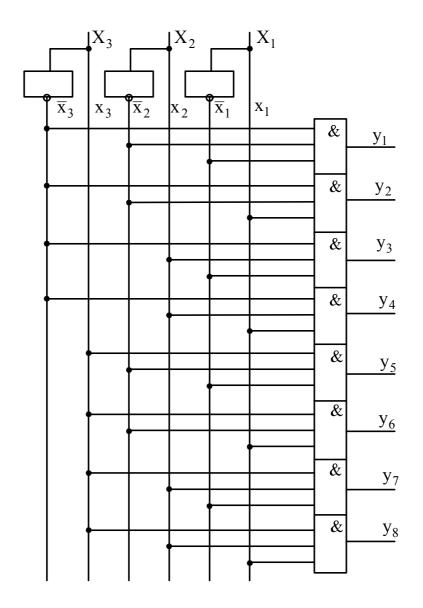

Рассмотрим дешифраторы с линейной выборкой, как наиболее распространенные.

Логическое уравнение для выходных переменных дешифратора празрядного числа по определению операции дешифрирования записывается в виде минтермов «конституент единицы» входных переменных:

$$\begin{aligned} y_1 &= X_n \cdot \overline{X}_{n-1} \cdot ... \cdot \overline{X}_2 \cdot \overline{X}_1 \\ y_2 &= \overline{X}_n \cdot X_{n-1} \cdot ... \cdot \overline{X}_2 \cdot \overline{X}_1 \\ ------ \\ y_n &= \overline{X}_n \cdot \overline{X}_{n-1} \cdot ... \cdot \overline{X}_2 \cdot X_1 \end{aligned}$$

Для примера таблица истинности для трехразрядного дешифратора:

Таким образом, на каждом выходе дешифратора появляется значение переменной, равное 1, лишь при одном наборе значений входных переменных.

Схема такого дешифратора строится на основе логических элементов **u** с n-входами, где n — число разрядов входного кода дешифратора. Например для рассмотренного трехразрядного дешифратора схема имеет следующий вид:

В данной схеме на соответствующую схему сравнения  $\boldsymbol{U}$  подаются соответствующие сигналы либо с прямых либо с инверсных значений переменной X. Так например для у4 сигналы подаются с линий  $\overline{X}_3$ ,  $X_2$ ,  $X_1$ . Таким образом можно сформировать дешифраторы с разрядностью 4; при этом 16 выходных линий; 5- при этом будет 32 выходные линии и т. д.

Соответственно потребуются 4 и 5 входовые логические элементы  $\mathbf{\textit{M}}$ . Однако составе ИМС, выпускаемых отечественной обычно отсутствуют промышленностью, логические элементы коэффициентом объединения по входу более восьми и этим значением ограниченна разрядность входных чисел линейного дешифратора. Часто управления устройствами

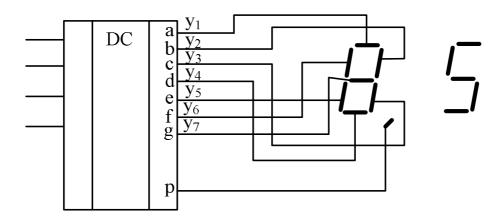

Часто дешифраторы применяют для управления устройствами отображения информации ( световыми табло, индикаторами и т. п.). При этом используется входной двоично-десятичный код, который дешифрируется в набор значений высокого уровня на нескольких выходах дешифратора, соединенных с соответствующими сегментами

индицируемого числа. Так например:

для того чтобы высветить на цифровом табло цифру 5 необходимо подать входной код 0101 и при этом на выходе получить комбинацию  $y_1y_2y_3y_4y_5y_6y_7 = 1011011$ .

Кроме того дешифраторы широко применяются в системах управления для формирования управляющих сигналов несколькими механизмами; в цифровых запоминающих устройствах для формирования выборки соответствующей ячейки памяти и т. п.