#### 2. МИКРОПРОЦЕССОРЫ

# 2.1. Успехи интегральной технологии и причины появления микропроцессоров

Интегральная технология (ИТ) за первые 20..30 лет своего развития достигла таких относительных темпов роста характеристик качества, которых не знала ни одна область человеческой деятельности (включая и такие бурно растущие, как авиация и космонавтика). Действительно, рассмотрим динамику изменений основных параметров ИТ за первые 20 лет ее развития (1960..1980гг):

- Степень интеграции N увеличилась на 5-6 порядков;

- Площадь транзистора S уменьшилась на 3 порядка;

- Рабочая частота f увеличилась на 1-3 порядка;

- Факторы добротности:

- 1)  $f \times N$  увеличился на 5-7 порядков;

- 2) Р×t уменьшился на 4 порядка;

где Р – мощность, рассеиваемая элементом;

- t задержка на элементе;

- Надежность (при сопоставлении элементо-часов) увеличилась на 4-8 порядков;

- Производительность технологии (в транзисторах) увеличилась на 4-6 порядков;

- Цена на транзистор в составе ИС уменьшилась на 2-4 порядка.

Если бы авиапромышленность в те же годы имела аналогичные темпы роста соответствующих показателей качества (стоимость-скорость-расход топлива = стоимость-быстродействие-рассеиваемая мощность), то "Боинг 767" стоил бы \$500, облетал земной шар за 20 мин. и расходовал на этот полет 10 л. горючего.

Успехи ИТ в области элементной базы позволяли "поглощать" кристаллом все более высокие уровни ЭВМ: сначала - логические элементы, потом - операционные элементы (регистры, счетчики, дешифраторы,...), далее - операционные устройства. Степень функциональной сложности, достигнутой в ИС, определяется особенностью технологии, разрешающей способностью инструмента, а также структурными особенностями схемы: регулярностью, связностью.

Кроме того, следует иметь в виду, что выпуск ИС был экономически оправдан лишь для функционально универсальных схем, обеспечивающих их достаточно большую тиражность.

С этой точки зрения интересно взглянуть на соотношение ИС логики и памяти в процессе эволюции ИС-СИС-БИС-СБИС. Первые ИС (степень

интеграции N - 101) были исключительно логическими элементами. При достижении N примерно 102 стали появляться наряду с операционными элементами первые элементы памяти - 16-64-128 бит. По мере дальнейшего роста степени интеграции память стала быстро опережать "логику", т.к. по всем трем параметрам имела перед логическими схемами преимущество. Действительно, структура накопителя ЗУ существенно регулярна (повторяемость элементов и связей по двум координатам), связность ее растет пропорционально логарифму объема (при увеличении объема памяти вдвое и сохранении без изменения способа доступа в БИС достаточно добавить лишь один вывод). Наконец, память "нужна всем" и "чем больше, тем лучше", особенно, если "больше, но за ту же (почти) цену".

Что касается ИС логики, то на уровне N=103 на кристалле можно уже размещать устройство ЦВМ (например, АЛУ, ЦУУ), но схемы логики (особенно управление) существенно нерегулярны, их связность (сильно зависящая от конкретной схемы) растет примерно пропорционально N, причем такие схемы, как правило, не являлись универсальными и не могли выпускаться большими тиражами (исключения - БИС часов и калькуляторов).

Рассмотренные выше основные элементы современных МП устройств имеют «жесткую» логику и не имеют возможность изменять свои внутренние свойства и выполняемые функции.

Следующий структурный уровень «универсальных вычислительных средств для специализированных применений» начинает формироваться на рубеже 70-х годов, когда успехи интегральной технологии конца 60-х годов привели к созданию БИС, и таким образом, впервые появилась реальная технологическая возможность создать универсальный процессор на одном кристалле.

Термин микропроцессор за рубежом связан с известной разработкой, которую фирма Intel выполнила в 1969г. по заказу одной из японских компаний. На одном из первых этапов разработки изготовитель предложил в место очередного специализированного набора БИС жесткой логики создать универсальный процессор на кристалле, который мог быть запрограммирован затем на выполнение заданных в спецификации заказчика функций. Фирма Intel завершила разработку первого МП в июне 1971 года.

Основной концепцией тогда являлось «создать стандартный логический блок, конкретное назначение, функцию которого можно было определить после его изготовления...». И, следовательно, ключ успеха МП в «быстром снижении стоимости в пересчете на выполняемую функцию, так как этот фактор всегда был основной движущей силой технологии...»

Другими словами стоимость аппаратных средств значительно стала меньше стоимости программных разработок.

Последовательная реализация принципа «универсального процессора для специализированных применений» привела к созданию МП, который

можно определить следующим образом:

-Микропроцессор-массовый универсальный преобразователь информации, основное назначение которого - рассредоточение машинного «интеллекта» до уровня блоков, узлов и отдельных деталей специализированных систем контроля и управления, с целью повышения их эффективности и расширения функциональных возможностей.

Разработка первого микропроцессора (МП) - попытка создать универсальную логическую БИС, которая настраивается на выполнение конкретной функции после изготовления средствами программирования. На подобную БИС - МП первоначально предполагалось возложить лишь достаточно произвольные управляющие функции, однако позже МП стал использоваться как элементная база ЦВМ последующих поколений. Появление МП вызвало необходимость разработки целого спектра универсальных логических БИС, обслуживающих МП: контроллеры прерываний и прямого доступа в память (ПДП), шинные формирователи, порты ввода/вывода и др.

# 2.2. Характеристики микропроцессоров и поколения их создания

Кратко перечислим основные характеристики микропроцессоров:

- разрядность;

- быстродействие (тактовая частота, время выполнения "короткой" команды;

- потребляемая мощность;

- технология (уровень логических сигналов);

- архитектурные особенности: система операций, способы адресации, наличие и организация подсистем прерываний и ПДП, объем и организация СОЗУ, конвейер операций, аппаратная поддержка системы виртуальной памяти и т.п.;

- структурные особенности: количество и назначение шин (стандарт интерфейса), внутренняя структура;

- число источников питания;

- число БИС в комплекте;

В первые десятилетия своего развития микропроцессоры было принято делить на поколения, причем границы поколений (разумеется, весьма условно) проводились по признаку технологии, освоенной на данном этапе эволюции МП. Рассмотрим кратко особенности первых трех поколений МП.

**Микропроцессоры 1 поколения**. Первый МП был разработан фирмой INTEL и выпущен в 1971г. на основе р-МОП технологии (i4004). В 1972 и 1973 годах этой же фирмой были выпущены модели i4040, i8008. Фирма

Rockwell выпустила модели МП PSS-4, PSS-8. Все они могут быть отнесены к МП 1 поколения, характеристиками которого являются:

- разрядность 4..8 бит;

- технология р-МОП;

- быстродействие (RR) 5..60 мкС;

- тактовая частота 200..800 КГц;

- совмещение шин адреса и данных;

- число вспомогательных ИС и СИС 15..50;

- подсистемы прерываний и ПДП отсутствуют.

Первые МП 1-го поколения - 4-разрядные приборы, использовались для организации десятичной арифметики (калькуляторы). Так, і4004 имел 4-разрядное АЛУ с блоком десятичной коррекции, 16 РОНов, внутренний трехуровневый стек. Объем адресного пространства 212 (возможен выбор одного из 4 банков такого размера). Система команд включала 46 команд: пересылки, ввод/вывод, сдвиги, арифметические команды.

В процессе эволюции МП первого поколения (МП-1) имело место увеличение разрядности (до 8) и некоторое расширение функций. Так, в i4040 добавлены логические операции, увеличен массив РОН (до24), введено одноуровневое прерывание. i8008 предназначался прежде всего для использования в системах управления. В нем, по сравнению с i4004, увеличена разрядность (до 8), добавлены логические команды, но исключен блок десятичной коррекции. Все МП-1 выпускались в стандартном 16-выводовом корпусе.

Микропроцессоры 2 поколения. Совершенствование технологии МОП, переход на n-МОП технологию привел к появлению МП второго поколения, которые отличались от МП-1 не только количественными характеристиками, но и качественно. В 1974г. был выпущен МП i8080, который стал первым и наиболее популярным МП второго поколения (МП-2). Он же положил начало семейству однокристальных МП, которому суждено было стать (и оставаться до настоящего времени) доминирующим на мировом рынке МП. Вслед за i8080 другими фирмами были выпущены МП со сходными (иногда несколько лучшими) характеристиками. Наиболее известными являются. Z80 фирмы Zilog и MS6800 (Motorola). Эти МП, как и i8080, имеют своих 16- и 32-разрядных "потомков". Характерными признаками МП-2 можно считать:

- переход на более прогрессивные технологии n-MOП и КМОП, позволившие повысить быстродействие МП до 2..2,5 МГц (200..500 тыс. операций RR), снизить потребление мощности (КМОП);

- значительные архитектурные отличия: расширение системы операций, использование широкого набора способов адресации (прямая, косвенная, относительная, безадресная, непосредственная),введены подсистемы

- прерываний и прямого доступа в память (ПДП), предусмотрен механизм универсального стека;

- структурные отличия: шины адреса и данных разделены, уменьшено число вспомогательных ИС и СИС.

МП-2 пришли на смену МП-1, значительно расширив сферу применения МП. Правда, МП-1 (по признаку технологии р-МОП) возродились позже в новом качестве - дешевых приборов бытовой электроники.

Другая судьба ожидала МП-2. Появившиеся микропроцессоры третьего поколения (МП-3) стали развиваться параллельно с МП-2, причем МП-2 легли в основу т.н. однокристальных МП и микро-ЭВМ, а МП-3 - секционированных многокристальных МП.

**Тремье поколение МП** связано со стремлением к увеличению быстродействия МПС и переходом на биполярные технологии - ТТЛ и ТТЛШ.

Исходя из соотношения  $dE \times dt = const$ ,

где dt - время переключения, dE - энергия переключения

очевидно, что повышение быстродействия связано с увеличением рассеиваемой мощности, а следовательно - к снижению степени интеграции кристалла. Первые МП-3 приборы были двухразрядными, что не приводило к увеличению производительности МП, хотя тактовая частота увеличивалась значительно (на порядок). Это обстоятельство повлекло значительные структурные изменения в МП-3 по сравнению с МП-2:

- микропроцессоры выпускаются в виде секций со средствами межразрядных связей, позволяющими объединять в одну систему произвольное число секций для достижения заданной разрядности. В состав секций включалось АЛУ, РОН и некоторые элементы УУ;

- устройство управления вынесено на отдельный кристалл (группу кристаллов), общий для всех процессорных секций;

- за счет резерва внешних выводов (малая разрядность) предусмотрены отдельные шины ввода и вывода данных, адреса, причем данные от разных источников вводились по различным шинам. Так, первый МП-3 i3000 (серия К589 отечественный аналог) имел три двухразрядные входные шины данных (от памяти, УВВ и УУ) и две выходные шины данных и адреса;

- кристаллы управления реализуют УУ с программируемой логикой, что позволяет достаточно легко реализовать практически любую систему команд на фиксированной структуре операционного устройства.

**Тенденции развития поколений**. В настоящее время технология не является решающим фактором классификации МП, ибо появились разновидности технологий одного типа, обеспечивающие очень широкий спектр характеристик МП, широкое распространение получили комбинированные технологии (например, И2Л + TTЛШ).

Современные микропроцессоры принято разделять на два больших класса: однокристальные и многокристальные. В свою очередь, однокристальные МП можно разделить на собственно микропроцессоры и однокристальные микро-ЭВМ.

Направление развития однокристальных МП - непрерывное наращивание вычислительной мощности процессора за счет увеличения разрядности, расширения системы команд, появления дополнительных функций - Кэш-памяти, конвейера операций, встроенных процессоров плавающей запятой, аппаратной поддержки виртуальной памяти и др.

Однокристальные микро-ЭВМ, сохраняя вычислительную мощность процессора практически неизменной (на уровне 8-разрядного МП), содержат на кристалле все элементы МПС: тактовый генератор, память программ и данных, контроллеры параллельного и последовательного ввода/вывода, контроллеры прерываний, таймеры, а некоторые микро-ЭВМ - АЦП и ЦАП и другие спец. средства (например, динамические схемы управления восьмисегментной индикацией). Такие БИС можно непосредственно подключать к периферийным устройствам для создания микро-ЭВМ или включать в контур управления.

Многокристальные микропрограммируемые МП используются как элементная база "больших" ЭВМ или специализированных средств, для которых характерны нетрадиционные параметры.

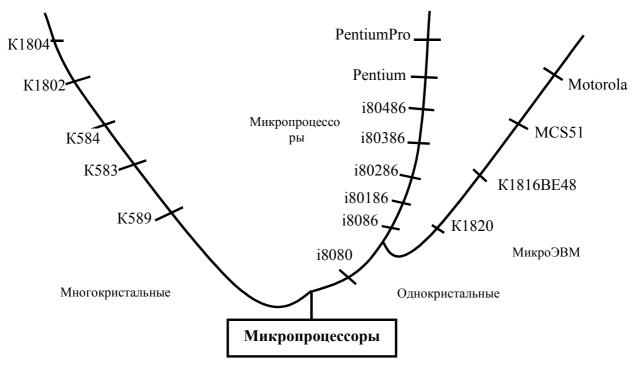

На Рис. 2.1 показаны направления развития различных типов МПС.

Из Рис. 2.1 видно, что наиболее многочисленное (и распространенное в мире) семейство микропроцессоров - INTEL. Далее будем иллюстрировать основные положения курса примерами организации МП этого семейства: однокристальные МП - i8080-i8086-i80286-i80386-i80486-Pentium-PentiumPro; однокристальные микро-ЭВМ - i8035-i8051/52

Рис. 2.1. Микропроцессоры (дерево развития)

#### 2.3. Классификация микропроцессоров

Бурное развитее микропроцессорной техники выделило из большого многообразия существующих МП три основные типы архитектуры МП:

- секционированные с наращиваемой разрядностью и микропрограммным управлением;

- однокристальные с фиксированной разрядностью и системой команд;

- однокристальные микроЭВМ.

Кроме того, МП могут быть классифицированы по ряду других признаков:

- по функциональному назначению: универсальные, применяемые в вычислительной технике и цифровой автоматике и специализированные, предназначенные для построения одного типа вычислительных машин или устройств автоматики (например, БИС МП микрокалькулятора);

- по разрядности обрабатываемых данных МП могут быть 2-, 4-, 8-, 12-, 16-, 24-, 32-разрядными;

- по способу управления МП можно разделить на МП со схемным и МП с микропрограммным управлением. Первые более быстродействующее, однако, их программирование однозначно определяется хранящимися в МП командами и электрической схемой. Вторые, при сравнительно меньшим быстродействием функционируют в зависимости от последовательности микрокоманд, установленных оператором.

• по используемой технологии: МП на основе ЭСЛ технологии – самые высокобыстродействующие (серия К1800); секционированные ТТЛШ МП наборы также обладают высоким быстродействием; МП на основе И2Л технологии обладают усредненными характеристиками; n-МДП технология обеспечивают самую высокую плотность компоновки и высокое быстродействие, однако имеет недостаточно широкий диапазон температур окружающей среды; КМДП(КМОП)-технология обеспечивает сверх низкое энергопотребление, высокую помехоустойчивость и наиболее приемлема для построения специализированных микропроцессорных систем для бортовых машин.

## 2.3. Восьмиразрядный микропроцессор КР580ВМ80

Процессор - центральное устройство ЭВМ, которое выполняет арифметические и логические операции, заданные программой преобразования информации, управляет вычислительным процессом и координирует работу периферийных устройств системы. Процессор, выполненный на одном кристалле методами интегральной технологии или на нескольких больших интегральных схемах БИС, называют микропроцессором.

Микропроцессоры широко используются для создания различных средств вычислительной техники и, в первую очередь, при разработке систем управления различными объектами. Родоначальником 8-разрядных микропроцессоров следует считать микропроцессор фирмы Intel i8080, созданный в 1974 г. Отечественным аналогом этого микропроцессора является КР580ВМ80А. Процессор оперирует с 8-битными данными и 16-битными адресами, что позволяет адресовать 64 Кбайта памяти.

Понятие "микро", в первую очередь, связано с размерами и стоимостью системы. Однако это понятие накладывает определенные ограничения и на возможности вычислительной системы; так, ограничена длина машинного слова микропроцессора, ограничены объем памяти и быстродействие.

Основные функции микропроцессора могут быть определены последовательностью пяти операций:

- 1. Считывание входного двоичного кода.

- 2. Сравнение считанного кода с внутренним состоянием процессора.

- 3. Вывод кода, являющегося результатом сравнения.

- 4. Изменение внутреннего состояния на новое состояние.

- 5. Повторение описанной последовательности действий для нового входного кода.

Основными функциональными элементами микропроцессора являются регистры и арифметико-логическое устройство. Операция сравнения реализуется как некоторая арифметическая или логическая операция в арифметико-логическом устройстве (АЛУ) микропроцессора. АЛУ может

осуществлять логическую и арифметическую обработку информации, представляемой в виде двоичных кодов.

Для хранения и передачи двоичных кодов используются регистры. Они состоят из нескольких запоминающих элементов емкостью один бит (триггеров), в которые информация записывается параллельно или последовательно. Буферным регистром с тремя состояниями называют электронную схему, предназначенную для отключения одной части микроЭВМ от другой. Эта схема работает подобно ключу. Выходы буферного регистра могут находиться в одном из трех состояний: 0, 1, высокоимпеансное состояние. Буферные регистры обычно могут передавать информацию в обоих направлениях: с входа на выход и с выхода на вход.

Связь между этими элементами осуществляется с помощью шин. Каждая шина состоит из отдельных линий связи. По линии связи можно передать один бит информации. Шины имеют разные функциональные назначение.

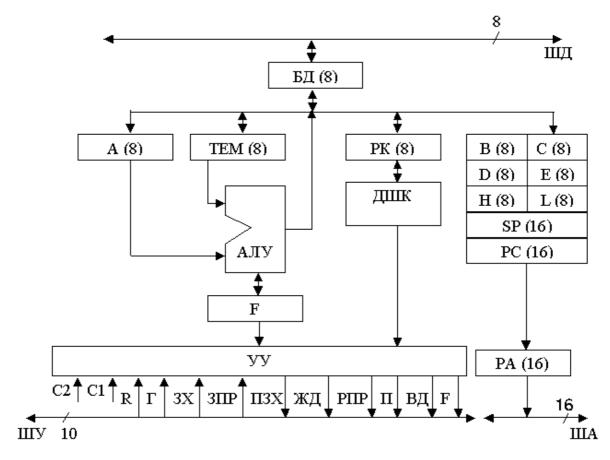

#### Структура микропроцессора

Микропроцессор в качестве своих элементов включает рассмотренные выше устройства и имеет весьма сложную электронную схему, содержащую около шести тысяч транзисторов. Однако, с точки зрения поль-

Рис. 2.2. Структура 8-разрядного микропроцессора

зователя и программиста, микропроцессор можно представить в виде сравнительно простой структуры, показанной на рис. 2.2. Эта структура относится к широко распространенному отечественному микропроцессору КР580BM 80A (аналог микропроцессора Intel i8080).

На рис. 2.2 обозначены следующие компоненты микропроцессора: БД – буфер данных, А— аккумулятор, ТЕМ— регистр временного хранения информации, АЛУ— арифметико-логическое устройство, F- регистр признаков, РК— регистр команды, ДШК— дешифратор команды, В,С,D,Е,Н,L — регистры общего назначения (РОН), SP— указатель стека, PC— счетчик команд, РА— регистр адреса (буферный), УУ— устройство управления, ШД—шина данных, ША—шина адреса, ШУ—шина управления.

Сигналы управления:

- С1,С2 (01,02) тактовые сигналы,

- R (RESET) сброс в исходное состояние,

- Г (READY) готовность внешнего устройства,

- 3X (HOLD) требование ВУ захвата шин,

- 3ПР (INT) запрос прерывания,

- ПЗХ (HLDA) подтверждение захвата,

- ЖD (WAIT) ожидание готовности ВУ,

- РПР (INTE) разрешение прерываний,

- П (DBIN) прием информации (чтение),

- ВД (WR) выдача информации (запись),

- F (SYNC) сигнал синхронизации.

Описываемый микропроцессор работает с двоичными числами длиной восемь бит или один байт. Такое число называется машинным оловом или данными D=D7D6D5D4D3D2D1D0, где D1- биты слова. Основными элементами макропроцессора являются арифметико-логическое устройство АЛУ; восьмиразрядные регистры A, B, C, D, E, H, L, TEM и PK; регистр признаков F; 16-разрядные регистры SP (указатели стека) и PC (счетчик команд); буферные регистры данных, адреса и устройство управления. При использовании микропроцессора не все из перечисленных элементов доступны программисту. В процессе составления программы могут использоваться только регистры A, B, C, D, E, H, L, TEM и PK.

Регистр A называется аккумулятором и используется для хранения одного из восьмиразрядных чисел, с которыми работает арифметикологическое устройство АЛУ. Эти числа называются операндами. Таким образом, в аккумуляторе всегда хранится один из операндов. Результат выполнения операции в АЛУ вновь помещают в аккумулятор. Шесть восьмиразрядных регистров (B, C, D, E, H, L) предназначены для хранения информации внутри микропроцессора и называются регистрами общего назначения (РОН). При выполнении некоторых команд регистры BC, DE, HL объединяются в регистровые пары для хранения 16-разрядных данных.

Регистр F называется регистром признаков результата выполнения операции в АЛУ. Он включает ряд триггеров, которые устанавливаются в "1" или сбрасываются в "0" в зависимости от некоторого признака получившегося в АЛУ результата выполнения операции. Каждый триггер хранит какой-то один признак. В регистре признаков хранятся следующие биты информации о признаках результата выполнения операции:

- Бит Z признак нуля; устанавливается в "1", если результат выполнения операции равен нулю (нули во всех разрядах восьмиразрядного кода данных);

- Бит S признак знака; устанавливается, если результат выполнения операции отрицателен;

- Бит P признак четности; устанавливается, если количество единиц в двоичном коде результата четное;

- $\bullet$  Бит C признак переноса; устанавливается, если в результате сложения двух восьмиразрядных чисел возникает перенос из старшего разряда или в результате вычитания возникает заем;

- Бит AC признак вспомогательного переноса; устанавливается, если перенос возникает из четвертого разряда D3 двоичного числа. Этот признак используется при операциях с четырехразрядными операндами.

Буферный восьмиразрядный регистр  $E\mathcal{I}$  данных позволяет вводить и выводить восьмиразрядные данные в микропроцессор или отключать его от внешней шины данных  $UU\mathcal{I}$ , 16-разрядный регистр адреса PA служит для временного хранения и вывода из микропроцессора 16-разрядного двоичного кода, являющегося адресом ячейки памяти или внешнего устройства.

Восьмиразрядный регистр *TEM* служит для временного хранения данных перед их передачей в АЛУ или в один из регистров процессора. Этот регистр недоступен программисту и на структурной схеме показан для детального пояснения взаимосвязей структурных элементов микропроцессора.

Регистр команды PK хранит двоичный код выполняемой команды. Так как этот регистр восьмиразрядный, то оказывается возможным различить  $2^8$ =256 кодов операций, что в большинстве случаев более чем достаточно. Код операции указывает, как происходит обработка данных при выполнении команды. Этот код декодируется дешифратором кода операции и совместно с устройством управления преобразуется в конкретные управляющие сигналы, реализующие запрограммированную команду.

Счетчик команд PC указывает, где в памяти расположен код данной команды, т.е. содержит адрес команды. Устройство управления YY увеличивает содержимое счетчика команд PC на единицу всякий раз, когда команда передается из памяти в процессор. Перед началом считывания команды счетчик команд PC уже содержит адрес текущей команды и имеет

16 разрядов, что позволяет различить  $2^{16}$ = 65536 адресов и, следовательно, использовать программы с большим числом команд.

16-разрядный указатель стека *SP* используется при необходимости изменения последовательности выполнения команд программы микропроцессором, например в случае использования подпрограммы, для запоминания адреса команды, к которой нужно вернуться после выполнения подпрограммы.

Устройство управления *УУ* является одним из важнейших блоков микропроцессора и обеспечивает необходимую последовательность всех действий элементов микропроцессора и микропроцессора в целом. После извлечения команды из памяти и ее дешифрирования устройство управления генерирует последовательность сигналов, необходимую для выполнения команды, а также самостоятельно реагирует на различные внешние сигналы. На рис. 2.2 обозначены входные и выходные сигналы устройства управления, связывающие микропроцессор с внешними устройствами. Назначение этих сигналов следующее:

- $C_1$ ,  $C_2$  входы тактирующих импульсов;

- $\bullet$  R установка нуля. Вход сигнала установки микропроцессора в исходное состояние;

- $\Gamma$  готовность. Вход сигнала о готовности внешнего устройства ввести или принять информацию по шине данных;

- 3X захват. Вход сигнала, означающего запрос внешнего устройства на предоставление ему магистральных шин;

- *ЗПР* запрос прерывания. Вход сигнала от внешнего устройства, информирующего микропроцессор о запросе на прерывание основной программы;

- $\Pi 3X$  подтверждение захвата. Выход сигнала реакции на захват, подтверждающий, что шины адресные и данных микропроцессора отключены от внешних магистралей;

- ЖД ожидание. Выход сигнала, свидетельствующего, что микропроцессор находится в состоянии ожидания;

- РПР разрешение прерывания. Выход сигнала, разрешающего прерывание основной программы;

- $\Pi$  прием. Выход сигнала, подтверждающего прием информации с магистрали данных в микропроцессор;

- $B\mathcal{I}$  выдача. Выход сигнала, подтверждающего выдачу байта информации на магистраль данных;

- F синхронизация. Выход сигнала, свидетельствующего о начале машинного цикла.

**Работа микропроцессора**, как и любого цифрового устройства, заключается в последовательной схеме состояний, каждому из которых соответствует некоторое определенное сочетание сигналов на всех линиях шин, входах и выходах элементов. Смена состояний обеспечивается подачей сигналов тактирования C1 и C2, каждый из которых является последовательностью прямоугольных импульсов. Одно состояние схемы микропроцессора длится в течение одного такта.

Определенное число тактов (от 3 до 5) образует машинный цикл. Машинный цикл обеспечивает выполнение некоторого простейшего действия микропроцессором: выборки кода команды из памяти и его дешифрации, выборки операнда из памяти и др. Цикл команды — это последовательность некоторых машинных циклов (от 1 до 5), выполнение которых обеспечивает исполнение команды.

Типичным машинным циклом является цикл выборки кода команды из памяти и его дешифрация. Каждый цикл начинается с выдачи микропроцессором сигнала синхронизации F и одновременного вывода на шину данных слова состояния, биты которого определяют особенности работы в осуществляемом цикле:

- $b_0$ : INTA подтверждение прерывания,

- b<sub>1</sub>: WO признак записи/вывода,

- b<sub>2</sub>: STACK признак работы со стеком,

- b<sub>3</sub>: HLTA признак остановки,

- b<sub>4</sub>: OUT признак вывода в порт,

- b<sub>5</sub>: M1 признак выборки первого байта команды,

- b<sub>6</sub>: INP признак ввода из порта,

- b<sub>7</sub>: MEMR признак обращения к памяти.

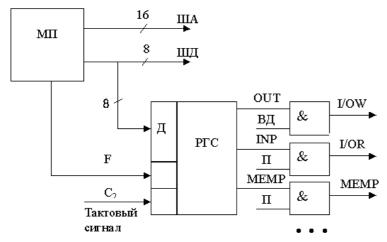

Из сигналов управления микропроцессора и битов слова состояния формируется расширенный набор системных управляющих сигналов.

Рис. 2.3. Формирование сигналов управления

Принцип формирования на примере нескольких сигналов поясняется схемой на рис. 2.3.

При выдаче микропроцессором  $M\Pi$  сигнала синхронизации F в регистр состояния  $P\Gamma C$  записывается слово состояния микропроцессора, присутствующее в этот момент на его шине данных  $UU\Pi$ . Запись тактируется сигналом  $C_2$ .

С помощью логиче-

ских схем «И» из значений бит слова состояния и сигналов управления микропроцессора формируются новые системные управляющие сигналы, расширяющие возможности управления:

- I/OW вывод данных на внешнее устройство,

- I/OR ввод данных из внешнего устройства,

- MEMR чтение из памяти,

| 10<br>9<br>8<br>7<br>3<br>4<br>5      | D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 | CPU | HIX X XD PHP H BD G F                                                | 21<br>24<br>16<br>17<br>18<br>19<br>25<br>26                  |

|---------------------------------------|----------------------------------------------|-----|----------------------------------------------------------------------|---------------------------------------------------------------|

| 13<br>14<br>12<br>28<br>20<br>11<br>2 | 3X<br>3IIP<br>R<br>12B<br>+5B<br>-5B<br>Oбщ  |     | A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11<br>A12<br>A13<br>A14<br>A15 | 31<br>32<br>33<br>34<br>35<br>1<br>40<br>37<br>38<br>39<br>36 |

Рис. 2.4. КР580ВМ80А

- MEMW запись в память,

- INTA подтверждение прерывания.

Конструктивно микропроцессор KP580BM80A оформлен В виде СБИС. имеющей 40 контактных выходов. На рис. 2.4 показано схемно-графическое изображение микропроцессора КР580ИК80А с указанием номеров контактных выводов и их назначения. Для работы микропроцессора необходимы три источника питания:  $U_1 = 12 \text{ B}, U_2 = 5$ В и  $U_3$  =-5 В. Общая потребляемая микропроцессором электрическая мощность составляет 1,5 Bt.

#### Системные шины

Связь микропроцессора с внешними устройствами осуществляется через системные шины, которые представляют собой набор соединительных проводников - линий, объединяющих одноименные выводы всех периферийных модулей. По каждой линии может быть передано значение одного разряда двоичного кода в виде уровней напряжения, со-

ответствующих логическому нулю или логической единице. По роду передаваемой информации все линии разделены на три группы, образующие: шину данных, шину адресов и шину управления.

Информация по шинам передается в виде двоичных кодов, длина которых определяется числом линий в шине. По шине данных передаются коды информационных сигналов, являющиеся данными для работы системы. Шина данных является двунаправленной шиной и позволяет передавать данные в любом направлении: от микропроцессора - к внешним устройствам и от внешних устройств – к микропроцессору.

|                                                              | Знач-     |

|--------------------------------------------------------------|-----------|

| Параметр                                                     | ние пара- |

|                                                              | метра     |

| Разрядность шины данных, бит                                 | 8         |

| Разрядность адресной шины, бит                               | 16        |

| Объем адресуемой памяти, Кбайт                               | 64        |

| Число команд                                                 | 78        |

| Максимальное число подключаемых внешних устройств ввода-     | 256/256   |

| вывода                                                       |           |

| Число каналов запроса прерывания                             | 8         |

| Производительность при выполнении операций вида регистр-     | 625       |

| регистр, тыс. операций в с                                   |           |

| Время выполнения команды вида регистр-регистр, мкс           | 1,6       |

| Ток утечки по входам, мкА                                    | 1         |

| Ток утечки на шинах адресной и данных, мкА                   | 10        |

| Время нарастания и спада напряжения на выводах микропроцес-  | 30        |

| сора, не более, нс                                           | 30        |

| Напряжение логической единицы тактирующих импульсов, не      | 10        |

| менее, В                                                     | 10        |

| Напряжение логического нуля тактирующих импульсов, не бо-    | 0,8       |

| лее, В                                                       |           |

| Входное напряжение логической единицы, не менее, В           | 3,3       |

| Выходное напряжение логической единицы, не менее, В          | 3,7       |

| Входное напряжение логического нуля, не менее, В             | 0,6       |

| Выходное напряжение логического нуля, не менее, В            | 0,45      |

| Предельная частота тактирующих импульсов, мГц                | 2,5       |

| Предельный выходной ток логической единицы, мА               | 0,1       |

| Предельный выходной ток логического нуля, мА                 | 1,8       |

| Пределы рабочей температуры окружающей среды, <sup>0</sup> C | -         |

| пределы расочен температуры окружающей среды, С              | 10+70     |

Шина адресов служит для выбора конкретного источника или приемника информации в каждой операции передачи данных. Число адресуемых внешних устройств определяется разрядностью кода адреса. Так, если для адресации используется 16-разрядный двоичный код, то можно адресовать  $2^{16} = 65536$  отдельных устройств или ячеек памяти.

По шине управления передаются логические сигналы управления, организующие совместную работу устройств, подключаемых к системным шинам.

Общие технические характеристики микропроцессора KP580BM80A приведены в табл. 2.1.

Для построения управляющих контроллеров находят применение и другие 8-разрядные микропроцессоры. Микропроцессор K1821BM85A

(аналог i8085) полностью совместим с KP580BM80A по системе команд, однако в отличие от последнего имеет встроенный генератор тактовых импульсов, встроенный контроллер прерываний, блок управления последовательным вводом-выводом, системный контроллер — шинный формирователь и требует только одного напряжения питания.

Микропроцессор Z80 фирмы Zilog также широко применяется в промышленных контроллерах. Этот микропроцессор совместим с i8080, но имеет более высокую тактовую частоту, двойной набор регистров РОН и расширенную систему команд. В микроконтроллерах находят также применение микропроцессоры других фирм.

### 2.4. Шестнадцатиразрядные микропроцессоры КР1810BM86 и КР1801BM1

Шестнадцатиразрядные микропроцессоры (МП) оперируют с 16-разрядными данными, имеют более сложную структуру, более высокую тактовую частоту, расширенные адресное пространство и систему команд, что обеспечивает лучшие характеристики, по сравнению с 8-разрядными микропроцессорами.

При построении микроЭВМ, персональных компьютеров и микроконтроллеров нашли применение 16-разрядные микропроцессоры фирм Intel (и их аналоги), Motorola и других. Представляет интерес рассмотрение особенностей построения таких микропроцессоров, поскольку они явились основой для построения современных 32-разрядных микропроцессоров, находящих широкое применение в промышленных компьютерах и программируемых микроконтроллерах.

## Микропроцессор КМ1810ВМ86

Наращивание возможностей МП достигается за счет увеличения разрядности машинного слова, увеличения объема основной памяти, увеличения быстродействия и расширения системы команд. Эти возможности реализованы в МП i8086, отечественным аналогом которого является КМ1810ВМ86. Данный МП имеет следующие характеристики.

Разрядность слова

— 16 бит,

Разрядность шины адреса

— 20 бит,

Объем адресуемой памяти

— 1 Мбайт,

Тактовая частота

— 5 МГц,

Быстродействие до -2,5 млн. оп./с.

Микропроцессор развивает основные решения 8-разрядного процессора и дополняет их новыми решениями. Расширен объем основной памяти, повышено быстродействие, введена очередь команд, разделены функции обработки информации и управления передачей информации и т.д.

МП выполнен в 40-контактном корпусе, имеет в своем составе около 29 тыс. транзисторов и требует одно напряжение питания +5В. Длина фи-

зического адреса памяти составляет 20 бит, что позволяет адресовать  $2^{20}$ =1 Мбайт памяти. Микропроцессор прямо адресует 256 портов ввода и 256 портов вывода, косвенно можно адресовать 64 К 8-битных портов вводавывода.

Система команд содержит 135 команд, при этом соблюдается совместимость снизу вверх с 8-разрядным микропроцессором i8080 (КР580ВМ80А). Предусмотрена возможность работы в мультипроцессорных системах.

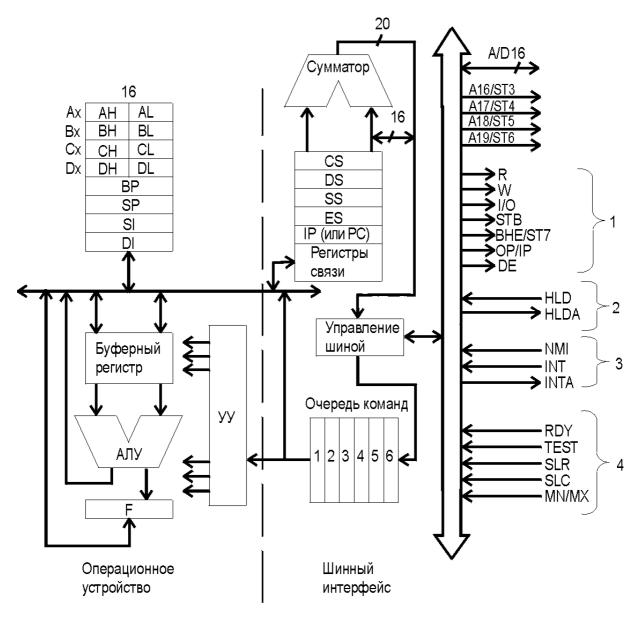

#### <u>Структура микропроцессора</u>

Структура микропроцессора показана на рис. 2.5. В состав микропроцессора входят два автономных устройства: операционное устройство и шинный интерфейс. Операционное устройство обеспечивает обработку информации и управление вычислительной системой. Шинный интерфейс

Рис. 2.5. Структура микропроцессора КМ1810ВМ86

выполняет все операции обмена данными с памятью и внешними устройствами. Поскольку оба эти устройства работают параллельно, то быстродействие системы в целом повышается. Все регистры в составе МП являются 16-разрядными.

Операционное устройство в своем составе имеет: устройство микропрограммного управления УУ; 16-разрядное арифметико-логическое устройство АЛУ; 16 разрядный регистр признаков F и восемь 16-разрядных регистров общего назначения РОН.

Устройство управления УУ считывает коды команд из очереди команд ОК, декодирует команды и вырабатывает последовательность микрокоманд, осуществляющих выполнение операции.

В АЛУ выполняются арифметические и логические операции над 8- и 16-разрядными числами с фиксированной запятой. Прямой связи между операционным устройством и внешней шиной нет. Операционное устройство обменивается данными только с шинным интерфейсом через регистры связи.

Признаки выполненных операций хранятся в регистре признаков F, который также является 16-разрядным (его называют также регистром флажков). Младший байт регистра флажков полностью соответствует регистру признаков 8-разрядного микропроцессора I8080 и включает следующие признаки операций:

- AF вспомогательный перенос (перенос или заем из младшей тетрады результата в старшую);

- CF перенос (перенос или заем в старшем бите b15 результата);

- SF знак, признак устанавливается при отрицательном результате;

- PF паритет, устанавливается при четном числе единиц в результате;

- ZF нуль, устанавливается при получении нулевого результата. Кроме этого имеются дополнительные признаки:

- OF –переполнение, сигнализирует о потере старшего бита результата;

- DF направление сканирования цепочек данных;

- IF флажок прерываний, разрешает или запрещает прерывания;

- TF флажок трассировки, переводит МП в одношаговый (покомандный) режим работы, который используется при отладке программ.

Состояние флажков учитывается в командах условного перехода. Кроме этого, имеются специальные команды, позволяющие изменять состояния отдельных флажков.

Также в составе операционного устройства имеются регистры общего назначения. Прежде всего, это регистры данных АХ, ВХ, СХ и DХ. Для этих регистров можно раздельно адресовать старший Н и младший L байты, что позволяет организовать обработку как 16-разрядных, так и 8-

разрядных данных. Регистры данных доступны программисту и предназначены для хранения данных при их обработке. Однако имеется ряд команд, которые специализируют регистры данных на определенные функции:

- AX аккумулятор;

- ВХ база (базовый адрес), аналог пары НС;

- CX счетчик;

- DX данные.

Группа адресных регистров SP,BP,SI и DI предназначена для хранения адресов (внутрисегментных смещений) и обеспечивает косвенную адресацию и динамическое вычисление эффективного адреса памяти. Эти регистры можно также использовать и как регистры общего назначения.

Регистры SP — указатель стека и BP — указатель базы предназначены для упрощения доступа к данным, находящимся в текущем сегменте стека.

Индексные регистры SI — индекс источника и DI — индекс приемника содержат смещения адресов источника и приемника данных, относящихся по умолчанию к текущему сегменту данных.

При программировании необходимо тщательно распределять эти регистры и следить за их использованием ввиду многофункционального назначения регистров.

Шинный интерфейс выполняет для операционного устройства все операции обмена. Данные передаются между МП и памятью или между МП и портами ввода-вывода по запросам операционного устройства. Когда операционное устройство занято выполнением команды, шинный интерфейс независимо инициирует выборку из памяти очередных команд и помещает их коды во внутреннюю память - очередь (буфер) команд длиной в 6 байт.

Как только в очереди команд освободятся 2 байта, шинный интерфейс выбирает очередные байты из памяти. Однако, если очередной командой является команда перехода, шинный интерфейс сбрасывает очередь и осуществляет ее новое заполнение, выбирая очередные байты по адресу перехода (реинициализация очереди команд).

Шинный интерфейс приостанавливает выборку команд, если операционное устройство запрашивает ввод-вывод информации из памяти или портов ввода-вывода. В целом такая организация работы сокращает время ожидания выборки очередной команды и повышает общее быстродействие МП.

В состав шинного интерфейса входят регистры связи с операционным устройством, адресные регистры, сумматор  $\Sigma$ , очередь команд (шесть 8-битных регистров) ОК и управляющее устройство. Адресные регистры и сумматор позволяют сформировать 20-битный физический адрес памяти из двух 16-битных логических адресов — сегмента (базы) и смещения.

#### Адресация памяти

Микропроцессор работает с памятью, которая организована в виде совокупности байтовых ячеек. С целью увеличения адресного пространства основной памяти принята адресация ячеек 20-битными адресными кодами. Такой код является физическим адресом ячейки памяти. Однако, поскольку микропроцессор работает с 16-битными кодами, то формирование физического 20-битного адреса осуществляется путем обработки 16-битных адресных кодов.

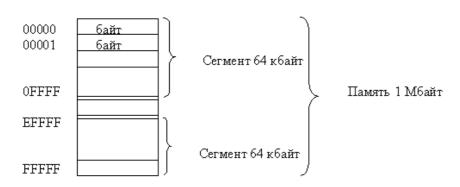

Для этого все пространство адресов памяти разбито на сегменты по 64

Рис. 2.6. Адресация ячеек памяти

Кбайта (рис. 2.6). Таких сегментов всего 16, следовательно, общий объем памяти

64 Кбайт × 16 = 1 Мбайт.

При адресации ячейки памяти, прежде всего, адресуется сегмент. Его адресация произ-

водится 16-разрядным двоичным кодом. Внутри сегмента ячейка памяти адресуется 16-битным кодом смещения. Таким образом, физический адрес памяти определяется суммированием адреса сегмента и внутрисегментного адреса ячейки памяти (внутрисегментного смещения).

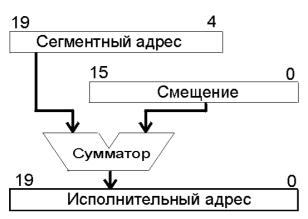

Рис. 2.7. Вычисление адреса

Вычисление физического 20битного адреса осуществляется в сумматоре путем суммирования сдвинутого адреса сегмента и адреса внутрисегментного смещения (рис. 2.7).

Адрес сегмента сдвигается влево на 4 бита, при этом предполагается, что младшие четыре бита равны нулю. Сумма сдвинутого адреса сегмента и смещения и дает 20-битный исполнительный адрес ячейки памяти. Таким образом, логическая раз-

метка памяти на сегменты произвольна при условии, что адреса сегментов кратны 16 (поскольку младшие 4 бита всегда равны нулю).

Любые два смежных байта в памяти образуют 16-битное слово. Первым в слове записывается младший байт. Адресом машинного слова является адрес младшего байта слова.

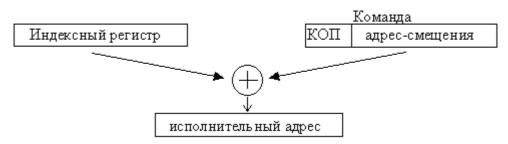

Система команд 16-разрядного МП использует в числе других относительную адресацию операндов, когда адрес операнда равен сумме некоторого базового значения адреса и смещения. Разновидностью относительной адресации является индексная адресация, при которой действительный адрес операнда находится прибавлением кода адреса, указанного в команде, к базовому адресу, хранимому в специальном индексном регистре (рис. 2.8).

Рис. 2.8. Относительная адресация

В памяти можно организовать 4 типа сегментов: сегмент кодов CS; сегмент данных DS; сегмент стека SS и сегмент экстракодов ES. Адресом каждого сегмента является адрес его первого байта в памяти. Реально этот адрес задается 16-битным кодом, однако рассматривается как 20-битный адрес, у которого младшие 4 бита всегда равны нулю. Таким образом, сегменты начинаются на 16-байтных границах памяти, называемых параграфами. Других ограничений на разбиение памяти на сегменты нет. Сегменты в памяти при ее логической организации могут частично или полностью перекрываться. Адреса логических сегментов хранятся в адресных регистрах сегментов CS, DS, SS и ES и используются при нахождении физического адреса ячейки памяти.

Физическая ячейка памяти может принадлежать одному или нескольким сегментам. Распределение сегментов в памяти осуществляется программным путем и может динамично изменяться. В каждый момент времени те сегменты, адреса которых находятся в регистрах сегментных адресов CS, DS, SS, ES, являются текущими и к ним происходит обращение.

Модификация содержимого сегментных регистров приводит к переключению сегментов в памяти. Это обычно требуется, когда 64 Кбайт для определенной информации недостаточно. Команды всегда выбираются из текущего сегмента кода, базовый адрес которого хранится в сегментном регистре CS, смещение в счетчике команд IP (PC).

#### Системная магистраль

Системная магистраль микропроцессора образуется 16-разрядной мультиплексной шиной "адрес/данные", шиной "старшие биты адресов/состояния" и шиной управления. По шине "адрес/данные" передаются младшие 16 бит физических 20-разрядных адресов ячеек памяти, адреса

внешних устройств и 16-битные данные. Для временной селекции адресов и данных служат сигналы стробирования, передаваемые по линиям шины управления.

Старшие 4 бита 20-разрядного адреса A16-A19 передаются по 4 отдельным мультиплексным линиям "адрес/состояния". Когда по этим линиям не передается адрес, то передаются сигналы, характеризующие состояние МП:

- ST3, ST4 идентификация используемого в операции сегментного регистра;

- ST5 состояние флажка прерываний;

- ST6 не используется (=0).

Все выводы микропроцессора (за исключением STB) имеют тристабильные выходные буферы.

Сигналы шины управления можно разбить на следующие функциональные группы.

- 1. Сигналы управления шиной.

- 2. Управление прямым доступом к памяти (ПДП).

- 3. Управление прерываниями.

- 4. Управление работой МП.

Назначение этих сигналов следующее:

- R (или RD) чтение. Ввод данных памяти или УВВИ;

- W (или WR) запись. Вывод данных из МП в память или УВВИ;

- $\bullet$  М/ІО память/УВВИ. Разделение адресного пространства памяти и ввода-вывода;

- STB (или ALE) строб адреса. Подтверждает наличие адреса на шине адрес/данные;

- BHE/ST7 разрешение старшего байта/состояние; ST7-не используется;

- OP/IP (или DT/R) передача/прием данных. Определяет направление передачи информации по шине данных и используется для управления шинными формирователями;

- DE- строб данных, для управления шинными формирователями;

- HLD (или HOLD) запрос (захват) шины;

- HLDA подтверждение захвата;

- NMI немаскируемое прерывание. Вызов программы обслуживания независимо от разрешения прерывания;

- INT запрос прерывания, маскируемое прерывание;

- INTA подтверждение прерывания и считывание вектора прерывания;

- RDY готовность внешнего устройства;

- TEST проверка, при TEST=1 МП входит в холостые состояния;

- CLR сброс в начальное состояние;

- CLC синхронизация (или тактирование);

- MN/MX минимальный/максимальный. Конфигурация МП (наличие сопроцессора).

Значение сигналов перечислено для одиночного использования микропроцессора (минимальный режим). Микропроцессор может использоваться и в мультипроцессорной системе (максимальный режим). В максимальном режиме изменяются значения 8 сигналов: HLD, HLDA, W, M/IO, OP/IP, DE, STB и INTA. Новые значения сигналов позволяют организовать взаимодействие нескольких процессоров между собой.

## Адресация внешних устройств

Адресное пространство ввода-вывода изолировано от адресного пространства памяти. В системе команд имеются специальные команды, которые обеспечивают передачу данных между регистрами МП и портами ввода-вывода.

Адресное пространство ввода-вывода составляет 64 К портов. Порты адресуются аналогично байтам и словам памяти, однако сегментные регистры при этом не используются. Для адресации портов используется косвенная адресация, т.е. используются адресные регистры. Первые же 256 портов ввода и 256 портов вывода адресуются непосредственно, так же как и в 8-разрядном процессоре.

При адресации портов ввода-вывода используются младшие 16 бит шины адреса. При прямой адресации первых 256 портов используется 8-битный адрес, который дублируется на младшей и старшей половинах шины адреса. Обмен информацией при вводе-выводе может вестись как словами, так и байтами. Возможен также ввод-вывод, отображенный на память.

## Работа микропроцессора

Для запуска и сброса микропроцессора предназначен сигнал CLR. При подаче этого сигнала микропроцессор прекращает свои действия, в счетчик команд записывается адрес (PC)=0000, в сегментный регистр кодового сегмента - (CS)=FFFF. Остальные сегментные регистры и регистр признаков сбрасываются. Очередь команд также сбрасывается. Таким образом, после сброса микропроцессор обращается к физическому адресу памяти FFFF0, по которому должна быть записана первая команда.

Останов микропроцессора происходит по команде HLT. Значение этой команды - «прекратить все действия до появления сигнала внешнего прерывания или сигнала сброса».

При работе микропроцессор циклически выполняет следующие действия:

- выборку команды из памяти и формирование адреса следующей команды;

- считывание операнда, если это требуется для выполнения команды;

- выполнение требуемой операции;

- запись результатов выполненной операции (если требуется) и переход к новому циклу.

Выполнение команды происходит за несколько машинных циклов. Первым следует цикл выборки команды из памяти, осуществляемый шинным интерфейсом. Каждый цикл состоит из последовательности тактов, которые синхронизируются с помощью тактовых импульсов частотой до 5 МГц, подаваемых на соответствующий вход микропроцессора.

## 16-разрядный микропроцессор К1801ВМ1

Микропроцессорный комплект БИС К1801 предназначен для построения микроЭВМ с системой команд «Электроника — 60М» и унифицированным интерфейсом по ОСТ 11.305.903-80. БИС центральных процессоров этого комплекта являются завершенными однокристальными микропроцессорами и жестко ориентированы на микропрограммную эмуляцию системы команд «Электроника — 60».

Комплект К1801 дополняется комплектом К1809, в который входят БИС для обслуживания периферийных устройств. В состав серии К1801 входят центральные микропроцессоры ВМ1, ВМ2 и ВМ3, причем каждый последующий имеет дополнительные возможности по сравнению с предыдущим.

Микропроцессор К1801ВМ1 предназначен для построения микро-ЭВМ. Имеет разрядность 16 бит как для данных, так и для адресов. Кристалл микропроцессора имеет размер 5х5 мм и содержит около 50 тыс. транзисторов. Тактовая частота микропроцессора до 5 МГц. Система команд включает 69 команд. Адресуемая память 64 Кбайт.

### Структура микропроцессора

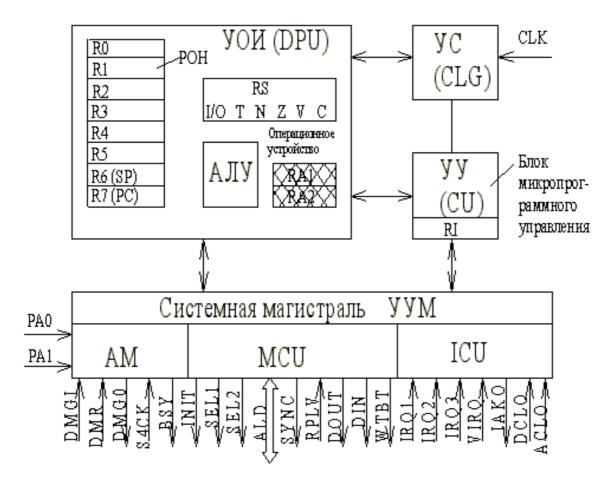

Структура микропроцессора показана на рис. 2.9. В состав микропроцессора входят: устройство обработки информации УОИ (DPU); устройство микропрограммного управления УУ (CU), содержащее в своем со ставе программируемую логическую матрицу и регистр команды RI; блок сопряжения с общей шиной МСU; блок обработки прерываний ICU; арбитр магистрали АМ и устройство синхронизации CLG.

Устройство обработки информации УОИ имеет в своем составе сверхоперативную память на 16-разрядных регистрах, из которых 8 программно доступны (R0-R7). При этом за регистрами R6 и R7 закреплены функции

Рис. 2.9. Структура микропроцессора К1801ВМ1

указателя стека SP и счетчика команд CK соответственно. Кроме этого, имеется арифметико-логическое устройство АЛУ и регистр состояний RS (регистр слова состояния процессора ССП). Биты этого регистра имеют следующее назначение:

- С признак переноса,

- V признак арифметического переполнения,

- Z признак нуля,

- N признак знака,

- Т признак прерывания по завершению команды,

- І/О установка приоритета (разрешение прерываний).

Операционный блок выполняет следующие функции:

- вычисление адреса и его временное хранение в регистре адреса,

- прием данных и их хранение в РОН,

- выполнение арифметических и логических операций,

- выдача данных в системную магистраль,

- формирование адресов векторов прерывания,

- формирование слова состояния МП (ССП).

Устройство микропрограммного управления управляет работой микропроцессора и имеет в своем составе регистр команды RI и программируемую логическую матрицу ПЛМ, в которой хранятся микропрограммы для всех команд микропроцессора. В этом блоке происходит расшифровка кода команды и преобразование ее в последовательность управляющих сигналов, обеспечивающих выполнение команды.

#### Системная магистраль

Системная магистраль формируется устройством управления магистралью УУМ. Она соответствует магистральному параллельному интерфейсу МПИ. Системную магистраль называют также системным каналом. Устройство управления магистралью УУМ можно разделить на три части.

- 1. Блок сопряжения с общей шиной MCU, обеспечивающий управление передачей информации между МП и внешними устройствами (память, устройства ввода-вывода). Сигналы этого блока имеют следующее назначение:

- INIT сброс внешних устройств в исходное состояние,

- SEL1, SEL2 выходы выборки регистров ввода/вывода 177716 и 177714,

- SYNC (строб адреса) выход синхронизации обмена,

- RPLY вход/выход синхронизации пассивного устройства,

- DOUT выход синхронизации записи,

- DIN выход синхронизации чтения,

- WTBT признак записи байта,

- А/D 16-разрядная шина адрес/данные.

- 2. Блок обработки прерываний ICU предназначен для организации приоритетной системы прерываний МП. Если одновременно возникло несколько запросов на прерывание, то в первую очередь обрабатывается прерывание с наивысшим приоритетом, остальные запоминаются и обрабатываются в порядке их приоритетов. Используется векторное прерывание. Сигналы управления прерываниями:

- IRQ (1 3) входы запросов прерываний,

- VIRQ вход требования прерывания,

- ІАКО выход предоставления прерывания,

- DCLO, ACLO входы аварии питания и сети.

- 3. Микропроцессор K1801BM1 может быть использован в мультипроцессорных системах, когда к общей магистрали подключено несколько процессоров. Для этого в составе микропроцессора имеется арбитр магистрали АМ, который обеспечивает обработку следующих сигналов:

- PA0, PA1 задание положения процессора в системе: главный/неглавный и его приоритета;

- DMGI вход разрешения прямого доступа к памяти (ПДП);

- DMGO выход разрешения ПДП;

- DMR вход требования ПДП для главного процессора, выход для подчиненного;

- $\bullet$  SHCK вход подтверждения выборки для главного, выход для подчиненного;

- BSY выход признака занятости канала.

## Адресное пространство микропроцессора

Все адресное пространство микропроцессора разбито на адреса ячеек памяти и адреса устройств ввода-вывода. Адреса и коды команд для этого микропроцессора принято указывать в восьмеричных кодах.

Адреса  $000000_8 - 157777_8$  — область ячеек памяти. В этом пространстве первые адреса  $000_8 - 377_8$  выделены для хранения векторов прерываний — адресов подпрограмм обслуживания прерываний.

Адреса  $160000_8 - 177777_8$  — область адресов портов ввода-вывода. По этим адресам располагаются регистры внешних устройств для вводавывода информации.

Таким образом, память занимает 56 Кбайт и 8 Кбайт занимают порты ввода-вывода. В системе команд отсутствуют специальные команды вводавывода информации из портов. Обращение к портам осуществляется так же, как и к ячейкам памяти. При этом можно анализировать данные, находящиеся в портах внешних устройств, не пересылая их в память или РОН, выполнять над ними арифметические и логические преобразования.

## Работа микропроцессора

Микропроцессор взаимодействует с системной магистралью или с системным каналом. Для выполнения любой команды микропроцессору требуется осуществить хотя бы одну операцию обращения к каналу. Первой операцией для всех команд является ввод кода команды из памяти. При этом адрес первой ячейки определяется счетчиком команд СК.

Все операции обращения к каналу для ввода-вывода называются циклами обращения к каналу. Существуют следующие стандартные циклы обращения к каналу: ВВОД, ВВОД – ПАУЗА – ВЫВОД, ВЫВОД, ВЫВОД БАЙТА. В промежутках между циклами обращения к каналу процессор может предоставлять канал устройству, запросившему ПДП.

Цикл ВВОД – ПАУЗА – ВЫВОД позволяет прочитать некоторые данные по заданному адресу, выполнить над этими данными арифметические или логические операции и вывести результат без повторения передачи адреса. Результат записывается по адресу последнего выбранного операнда.

Микропроцессор имеет развитые средства, обеспечивающие его работу в режиме прерываний. Прерыванием называется временное прекращение выполнения текущей программы и переход к выполнению программы обслуживания устройства, вызвавшего прерывание.

Каждое устройство, требующее прерывание, имеет программу обслу-

живания, вход в которую осуществляется автоматически с помощью вектора прерывания. Этот вектор указывает номер ячейки памяти, содержащей начальный адрес программы обслуживания прерывания.

## 2.5. Секционированные микропроцессоры

В развитие идеи микропроцессоров 3 поколения достаточно широкое распространение получили комплекты секционированных микропроцессорных БИС, на базе которых разрабатываются МПС с разрядно-

модульной организацией. Часто микропроцессоры такого типа называют многокристальными, имея в виду, что аппаратура МП располагается на нескольких связанных между собой кристаллах.

Однако, главной особенностью архитектуры многокристальных МП является раздельная организация операционного и управляющего автоматов и реализация операционной части в виде разрядных сечений.

При этом пользователь (разработчик) получает две глобальные степени свободы:

- \* возможность варьировать разрядность МПС за счет объединения различного числа БИС операционных устройств;

- \* возможность реализации (почти) произвольной системы команд за счет изменения содержимого микропрограммного ПЗУ.

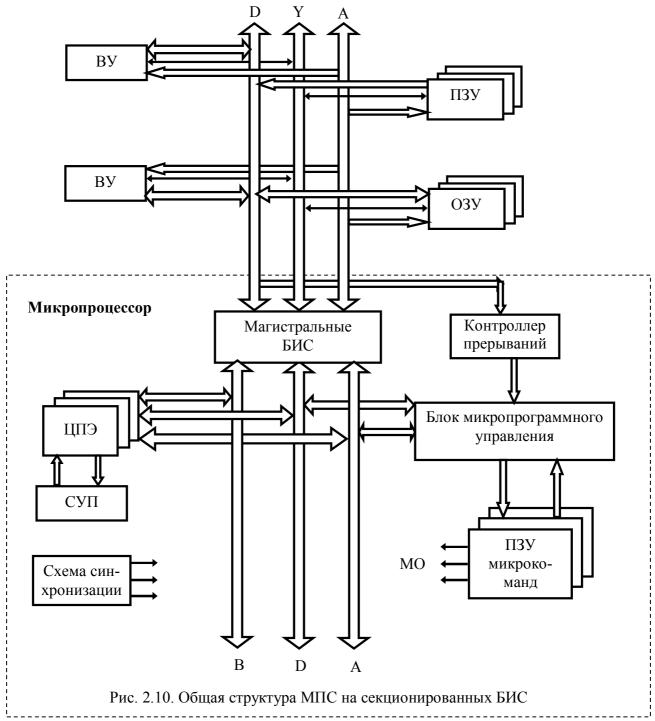

На **Ошибка! Источник ссылки не найден.**0 приведена общая структура МПС с разрядно-модульной организацией. Процессор реализован на комплекте секционированных БИС, а память и ВУ - традиционным для однокристальных МП способом.

Для реализации МПС с разрядно-модульной организацией в составе комплектов микропроцессорных БИС выпускаются различные варианты арифметико-логических секций, секций управления и вспомогательных БИС (регистры, схемы ускоренного переноса, контроллеры прерываний и др.).

## 2.5.1. Арифметико-логические секции

Для реализации операционного автомата МП используются арифметико-логические секции (АЛС) различной разрядности, иногда называемые центральными процессорными элементами (ЦПЭ).

Действительно, помимо непременного арифметико-логического блока со средствами межразрядных связей, в состав АЛС/ЦПЭ часто включаются регистры (специальные и общего назначения), средства коммутации магистралей, блоки позиции, дешифраторы инструкций и др. От процессора такие БИС отличает лишь отсутствие устройства управления.

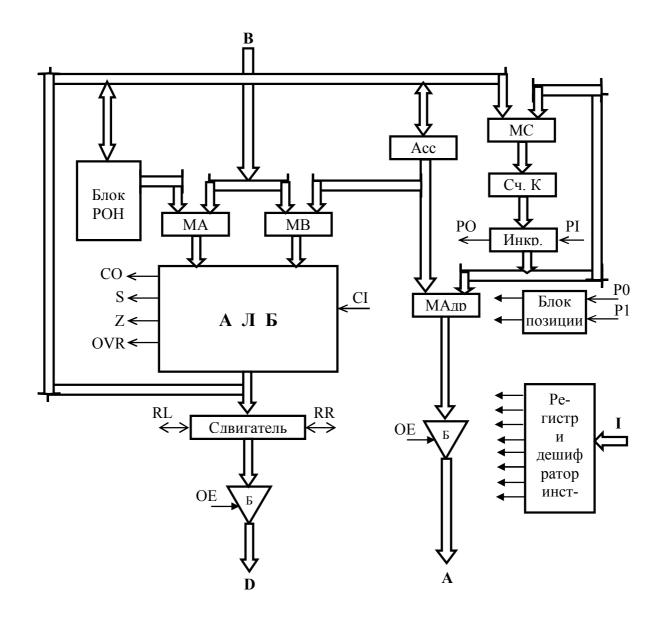

Наибольшее распространение получили ЦПЭ с т.н. трехшинной организацией (Ошибка! Источник ссылки не найден.11).

В состав ЦПЭ входят следующие основные блоки: арифметикологический блок АЛБ, блок регистров общего назначения РОН, мультиплексоры данных МА, МВ и МС, мультиплексор адреса МАдр, накапливающий регистр - аккумулятор Ас, двунаправленный сдвигатель, счетчик команд Сч.К с инкрементором Инкр., регистр и дешифратор микрокоманды (микроинструкции) и блок позиции.

Рис.2.11. Обобщенная структура ЦПЭ

Блок позиции предназначен для определения некоторых функций и назначения выводов секции в зависимости от ее положения в разрядной сетке процессора. Как правило, различают три позиции секции: младшая, средняя и старшая. Блок позиции присутствует не во всех вариантах АЛС.

Секция ЦПЭ имеет следующие входы: данных B, микроинструкции МК, переноса в АЛБ (CI) и в Сч.К (СК), кода позиции П0,П1.

Выходами БИС являются: шины данных D и адреса A, переносы из старших разрядов АЛБ и инкрементора СчК, флаги, формируемые в АЛБ (Z, P и др.).

Кроме того, в секции предусмотрены двунаправленные линии левого и праволо сдвига (СЛ и СП соответственно).

Разрядность секции ЦПЭ может быть различной (2 - 4 - 8 бит), причем наличие входов и выходов переносов АЛБ и инкрементора Сч.К, а так же двунаправленных линий правого и левого сдвигов дает возможность объединения произвольного числа секций.

Структуре **Ошибка! Источник ссылки не найден.**11 наиболее полно отвечают процессорные секции К584ВМ1 и К589ИК02. Популярнейшая серия секционированных БИС - К1804 (Ат2900) имеет несколько отличную структуру (**Ошибка! Источник ссылки не найден.**12, Рис.2.13).

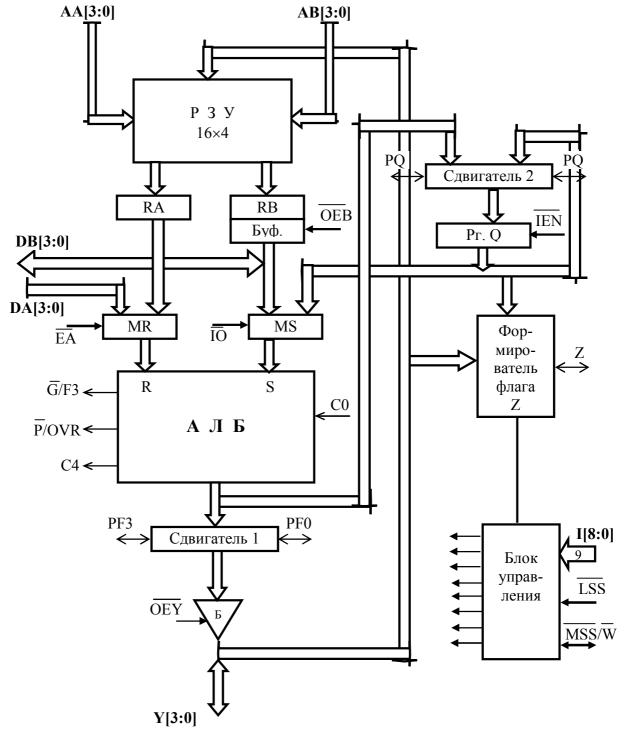

На **Ошибка! Источник ссылки не найден.**12 представлена 4-разрядная арифметико-логическая секция К1804ВС1 (Am2901). Она включает в себя :

- \* арифметико-логический блок АЛБ;

- \* двухканальное регистровое запоминающее устройство (РЗУ) объемом 16 4-разрядных слов;

- \* выходные регистры каналов РЗУ А и В;

- \* пятивходовой селектор источников данных, формирующий значения операндов R и S для АЛБ;

- \* селектор выходных данных, выбирающий для подачи на выходной буфер результат F с выхода АЛБ или считанное по каналу А РЗУ содержимое Рг.А;

- \* 4-разрядный регистр Q, который удобно использовать для хранения операндов в операциях умножения и деления;

- \* два сдвигателя, каждый из которых позволяет сдвинуть входной код на один разряд влево или вправо или передать операнд на выход без сдвига. Сдвигатель\_1 предназначен для сдвига результата операции в АЛБ при занесении его в РЗУ; сдвигатель\_2 позволяет сдвинуть содержимое регистра Q;

- \* блок дешифрации инструкции, выходы которого (микрооперации) управляют выбором операндов для АЛБ, действием в АЛБ и размещением результата.

Линии, связывающие секцию с "внешним миром" делятся на входные, выходные и двунаправленные:

```

D[3:0]

- вход данных;

AA[3:0],

- входы адресов каналов А и В РЗУ;

AB[3:0]

I[8:0]

- вход инструкции;

C0

- вход переноса в АЛБ;

OE/

- разрешение выдачи данных на выход буфера;

Y[3:0]

- выход данных;

- выход переноса из АЛБ;

C4

- выход признака нулевого результата;

Z

OVR

- выход признака арифметического переполнения;

```

G, P - выходы признаков генерации и прохождения переноса через тетраду; PR3, PR0 - двунаправленные линии (старшая и младшая) сдвигателя результата; PQ3, PQ0 - то же для сдвигателя регистра Q. AA[3:0] AB[3:0] PR0 PR3 Сдвигатель 1 PQ Сдвигатель 2 Р 3 У 16×4 Рг. Q D[3:0] 0000 MB MA D A 0 В Q Де-R шифра- $\overline{P} \leftarrow$ C0тор OVR**← А** Л **Б** инст-Z< рукции F3**←** Селектор вых. дан-<del>OE</del>

Рис.2.12. АЛС К804ВС1

Y[3:0]

Девятибитовая инструкция **I** делится на три трехбитовых поля, причем I[2:0] определяет выбор операндов для АЛБ, I[5:3] задает операцию в АЛБ, а I[8:6] управляет размещением результата. В таблице 2.2 приведена кодировка полей инструкции и описание соответствующих действий.

В АЛС 1804ВС1 управление осуществляется на уровне микрокоманд, уровень микроопераций в этой секции недоступен. Кроме того, секции ВС1 не различаются по позициям, занимаемым в процессоре.

Таблица 2.2

| Код  | Источник АЛБ |   | Операция                | Размещени           | е результата              |   |

|------|--------------|---|-------------------------|---------------------|---------------------------|---|

| поля | R            | S | в АЛБ                   | РЗУ (АВ)            | Рг. Q                     | Y |

| 000  | A            | Q | R + S + C0              | -                   | $F \rightarrow Q$         | F |

| 001  | Α            | В | S - R - 1 + C0          | -                   | -                         | F |

| 010  | 0            | Q | R - S - 1 + C0          | $F \rightarrow P3Y$ | -                         | A |

| 011  | 0            | В | $R \vee S$              | $F \rightarrow P3Y$ | -                         | F |

| 100  | 0            | A | R & S                   | F/2→ P3У            | $Q/2 \rightarrow Q$       | F |

| 101  | D            | A | R\ & S                  | F/2→ P3У            | -                         | F |

| 110  | D            | Q | $R \oplus S$            | 2·F→ P3У            | $2 \cdot Q \rightarrow Q$ | F |

| 111  | D            | 0 | $(R \oplus S)\setminus$ | 2·F→ P3У            | -                         | F |

Значительно большими функциональными возможностями обладает АЛС K1804BC2 (Am2903) (рис 2.13). Расширение возможностей обеспечено, с одной стороны, значительно более сложным АЛБ, с другой стороны возможностью непосредственного доступа ко многим точкам управления на кристалле.

Структуры секций. .BC1 и. .BC2 похожи друг на друга, однако некоторые, на первый взгляд незначительные отличия существенно расширяют возможности АЛС. .BC2. Отметим отличительные особенности структуры. .BC2.

1) Регистр канала В РЗУ снабжен буфером с тремя состояниями, выход которого поступает на вход мультиплексора MS и на внешние линии DB[3:0], а управление буфером доступно пользователю непосредственно с помощью сигнала OEB\.

При открытом буфере считанное по каналу В содержимое ячейки РЗУ поступает на вход мультиплексора MS и может быть использовано в качестве операнда АЛУ. Одновременно содержимое Рг.В поступает на выходные линии DB и может быть использовано внешними схемами, т.е. имеется непосредственный доступ в РЗУ по каналу В.

При закрытом буфере линии DB становятся дополнительными входными, наряду с линиями DA[3:0].

2) Сдвигатель результата F так же снабжен буферной схемой, управляемой сигналом ОЕУ\, причем вход РЗУ соединен с выходом буфера, что позволяет использовать линии DY[3:0] как двунаправленные, обеспечи вая

при закрытом буфере непосредственный доступ в РЗУ по каналу записи В.

Рис.2.13. АЛС К804ВС2

Такая организация РЗУ позволяет расширять объем памяти, доступной секции, за счет подключения дополнительных внешних модулей памяти, а так же обеспечивать прямой доступ в РЗУ со стороны других абонентов. Характерно, что сигнал управления записью в РЗУ - WE\ - так же доступен пользователю.

Помимо буферных схем, непосредственному управлению доступны

мультиплексоры операндов АЛУ MR и MS и загрузка результата в регистр RQ. В секции предусмотрены входные сигналы позицирования. Ниже приведен список внешних линий секции и описано назначение линий:

DA[3:0] - входная шина данных;

DB[3:0] - двунаправленная шина данных;

DY[3:0] - шина результата (входная шина РЗУ); WE\ - разрешение записи в РЗУ (канал В);

EA\ - разрешение передачи A  $\rightarrow$  R (при EA = 1 D  $\rightarrow$  R);

IO - управление выбором  $DB \rightarrow S$  или  $B \rightarrow S$ ;

OEY\ - разрешение выдачи результата на линии Y[3:0];

IEN\ - разрешение записи в регистр Q;

PF3, PF0 - двунаправленные линии сдвигателя результата;PQ3, PQ0 - двунаправленные линии сдвигателя регистра Q;

С0 - входной перенос АЛУ; С4 - выходной перенос АЛУ;

P/OVR - признак прохождения переноса/флаг переполнения;

G/F3 - признак генерации переноса/флаг знака; LSS - вход задания младшей позиции БИС;

MSS/W - вход задания старшей позиции/выход строба записи в

РЗУ;

Z - флаг нуля или вход управления;

I[8:0] - код микрокоманды.

В БИС старшей позиции на выходах флагов АЛУ генерируются значения OVR и F3, на остальных позициях - сигналы P и G для подключения схемы ускоренного переноса. Если LSS = 0 (младшая позиция), то линия MSS/W становится выходом W, на котором формируется строб записи в P3У. Позиция секции задается кодом на LSS и MSS, указанном в табл. 2.3.

Таблица 2.3

| LSS | MSS | Позиция |

|-----|-----|---------|

| 0   | X   | Младшая |

| 1   | 0   | Средняя |

| 1   | 1   | Старшая |

Система микрокоманд. ЦПЭ управляется 20-разрядной микрокомандой, включающей поля адресов AA[3:0] и AB[3:0], инструкцию I[8:0] и специальные управляющие сигналы EA, IO, OEB.

Выбор источников операндов для АЛУ обеспечивается набором внешних управляющих сигналов (

Таблица 2.)

Таблица 2.4

| Управляющие сигналы |    |     | Операнд | ды АЛУ |

|---------------------|----|-----|---------|--------|

| EA                  | IO | OEB | R       | S      |

| 0                   | 0  | 0   | RA      | RB     |

| 0                   | 0  | 1   | RA      | DB     |

| 0                   | 1  | X   | RA      | RQ     |

| 1                   | 0  | 0   | DA      | RB     |

| 1                   | 0  | 1   | DA      | DB     |

| 1                   | 1  | X   | DA      | RQ     |

Поле инструкции I[4:1] определяет операцию в АЛУ (Характерно, что действия, определяемые табл. 2.5 и 2.6 соответствуют значению сигнала IEN = 0, иначе запись в регистр RQ блокируется.

Назначение линий PF3, PF0, PQ3, PQ0 (вход, выход, высокоимпеансное состояние) и их значения определяются выполняемым типом сдвига, позицией секции и выполняемой микрооперацией. Подробно о состоянии этих линий в различных операциях сказано в [15], [16], [5], [6].

Синхронизация работы секции осуществляется от однофазного тактового сигнала Т, период которого не должен быть менее 80 нс.

Помимо арифметико-логических секций, в рамках серии К1804 выпускаются 16-разрядные несекционированные процессорные элементы, архитектура которых значительно отличается от рассмотренных выше.

Таблица 2.5), а поле I[8:5] - выбор приемников результатов (), причем если (I[4:1] = 0000) & (IO = 0), то в АЛУ выполняется специальная функция (Ошибка! Источник ссылки не найден.6).

При выполнении специальной функции действия в АЛУ зависят не только от кода I[8:5], но и от состояния входа Z. Специальные функции могут обеспечить выполнение умножения и деления чисел без знаков или в дополнительном коде. Естественно, что по одной микрокоманде осуществляется умножение на один разряд множителя или получение одной цифры частного. Микрокоманды, включающие специальные функции, фактически составляют тело цикла операции умножения или деления.

Кроме того, специальные функции позволяют осуществлять нормализацию слов одинарной и двойной длины.

Сдвигатель F результата может выполнять 4 типа сдвига: левый SLL и правый SLR логический и левый SAL и правый SAR арифметический. При арифметических сдвигах старший разряд F3 старшей секции (знаковый) не участвует в сдвиге. Кроме того, сдвигатель F реализует при I[8:5] = 1110 т.н. "расширение знака", при котором на все линии DY[3:0] поступает зна-

чение PF0. При I[8:5] = 10хх на линию PF0 выдается значение паритета: PF0 = F0 +' F1 +' F2 +' F3 +' PF3. Сдвигатель Q выполняет только логические сдвиги. При определенных комбинациях кода инструкции сдвигатели передают входную информацию на выход без сдвига.

Характерно, что действия, определяемые табл. 2.5 и 2.6 соответствуют значению сигнала IEN = 0, иначе запись в регистр RQ блокируется.

Назначение линий PF3, PF0, PQ3, PQ0 (вход, выход, высокоимпеансное состояние) и их значения определяются выполняемым типом сдвига, позицией секции и выполняемой микрооперацией. Подробно о состоянии этих линий в различных операциях сказано в [15], [16], [5], [6].

Синхронизация работы секции осуществляется от однофазного тактового сигнала Т, период которого не должен быть менее 80 нс.

Помимо арифметико-логических секций, в рамках серии К1804 выпускаются 16-разрядные несекционированные процессорные элементы, архитектура которых значительно отличается от рассмотренных выше.

Таблица 2.5 Таблица 2.6

| T[/.1] | Финист АПУ              | 1[0.5] | C-ry E             | C==== 0              |

|--------|-------------------------|--------|--------------------|----------------------|

| I[4:1] | Функция АЛУ             | I[8:5] | Сдвиг. Г           | Сдвиг.Q              |

| 0000   | 1111                    | 0000   | SAR                | ı                    |

| 0001   | S - R - 1 + C0          | 0001   | SLR                | 1                    |

| 0010   | R - S - 1 + C0          | 0010   | SAR                | SLR                  |

| 0011   | R + S + C0              | 0011   | SLR                | SLR                  |

| 0100   | S + C0                  | 0100   | $F \rightarrow DY$ | -                    |

| 0101   | S/ + C0                 | 0101   | $F \rightarrow DY$ | SLR                  |

| 0110   | R + C0                  | 0110   | $F \rightarrow DY$ | $F \rightarrow RQ$   |

| 0111   | R\ + C0                 | 0111   | $F \rightarrow DY$ | $F \rightarrow RQ$   |

| 1000   | 0000                    | 1000   | SAL                | -                    |

| 1001   | R\ & S                  | 1001   | SLL                | 1                    |

| 1010   | $(R \oplus S)\setminus$ | 1010   | SAL                | $\operatorname{SLL}$ |

| 1011   | $R \oplus S$            | 1011   | SLL                | SLL                  |

| 1100   | R & S                   | 1100   | $F \rightarrow DY$ | -                    |

| 1101   | (R & S)\                | 1101   | $F \rightarrow DY$ | SLL                  |

| 1110   | (R ∨ S)\                | 1110   | расш.знака         | -                    |

| 1111   | $R \vee S$              | 1111   | $F \rightarrow DY$ | -                    |

В состав ПЭ К1804ВМ1 входит 16-разрядное АЛУ, блоки регистров, схемы управления и коммутации. Управление процессорным элементом осуществляется с помощью инструкций.

#### 2.5.2. Секции управления и устройства управления

Все управляющие устройства в составе многокристальных микропроцессоров реализуются как устройства управления с программируемой логикой (УУПЛ), классическая структура которых подробно описана в литературе, например.

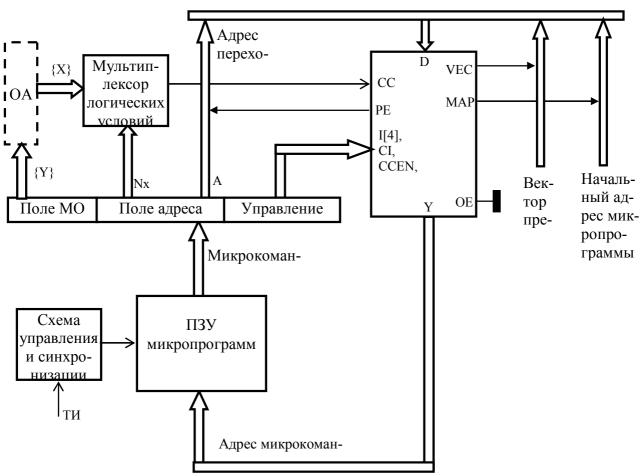

УУПЛ включает в себя ПЗУ микрокоманд, регистр микрокоманд с дешифраторами микроопераций и схему формирования адреса микрокоманды (СФАМ). Последняя представляет собой наиболее сложную и нерегулярную часть УУПЛ, причем структура СФАМ во многом определяет функциональные возможности УУПЛ.

Рассмотрим варианты организации СФАМ и их реализацию на различных типах БИС.

Эволюция структур СФАМ.

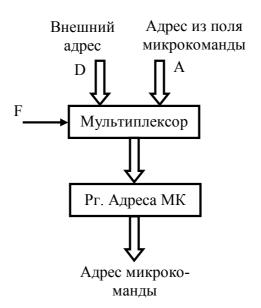

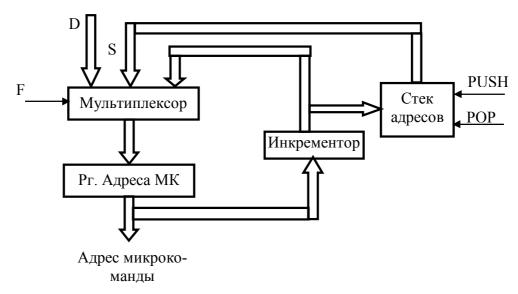

1) Простейшей дисциплиной адресации микрокоманд является принудительная, когда в составе каждой считанной из ПЗУ микрокоманды (МК) находится поле (А), содержащее адрес следующей МК.

Использование принудительной адресации (рис 2.14) предоставляет разработчику широкие возможности по размещению МК в ПЗУ, однако при этом не исключается повторение МК и даже участков микропрограмм, что приводит к нерациональному использованию памяти.

Начальный адрес микропрограммы (D) задается извне, а специальное поле МК (F) определяет источник адреса.

Рис.2.14. Принудительная адресация микрокоманд

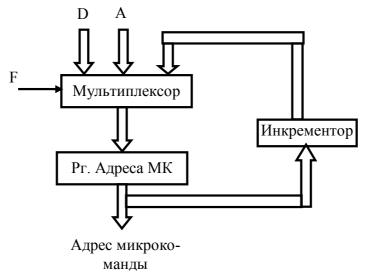

2) Организация последовательности адресов путем инкрементирования текущего адреса не требует выделения специального поля А в МК, но накладывает ограничение на расположение микрокоманд в памяти - последовательно выполняемые МК должны располагаться в соседних ячейках. В этом случае, например, для реализации умножения как линейной микропрограммы потребуется п или 2·п МК (n - разрядность операндов).

Сочетание вариантов адресации (1) и (2) позволяет осуществлять адресацию с инкрементом на линейных участках микропрограмм и принудительную адресацию на переходах (Ошибка! Источник ссылки не найден.14). При этом операционные МК и МК переходов должны иметь разные форматы.

3) Для организации модульного микропрограммирования полезно ввести в состав СФАМ стек адресов (Ошибка! Источник ссылки не найден.16). При этом появляется возможность использовать одни и те же микроподпрограммы при выполнении различных команд, что резко сокращает объем используемого ПЗУ.

Сочетание вариантов адресации (1) и (2) позволяет осуществлять адресацию с инкрементом на линейных участках микропрограмм и принудительную адресацию на переходах (Ошибка! Источник ссылки не найден.15). При этом операционные МК и МК переходов должны иметь разные форматы.

Сочетание вариантов адресации (1) и (2) позволяет осуществлять адресацию с инкрементом на линейных участках микропрограмм и принуди - тельную адресацию на переходах (Ошибка! Источник ссылки не найден.15). При этом операционные МК и МК переходов должны иметь разные форматы.

Рис.2.15. Адресация с инкрементом

Рис.2.16. Использование стека адреса

- 3) Для организации модульного микропрограммирования полезно ввести в состав СФАМ стек адресов (Ошибка! Источник ссылки не найден.16). При этом появляется возможность использовать одни и те же микроподпрограммы при выполнении различных команд, что резко сокращает объем используемого ПЗУ.

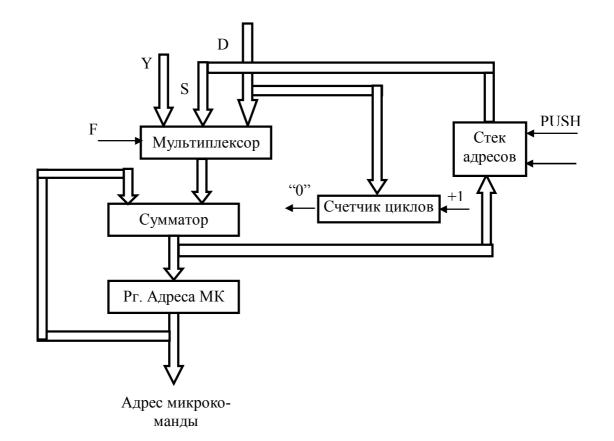

- 4) Следующий шаг в развитии архитектуры СФАМ замена инкрементора полноразрядным сумматором и введение в состав СФАМ счетчика циклов (Рис.2.17). Наличие сумматора позволяет осуществлять смещение адресов МК на произвольное число ячеек, задаваемое по шинам D или Y. Это позволяет программисту индексировать самоперемещающиеся микропрограммы.

Рис.2.17. СФАМ с полноразрядным сумматором и счетчиком циклов

Наличие счетчика циклов позволяет существенно сократить затраты памяти и времени при обработке циклических микропрограмм.

В серийно выпускаемых БИС, предназначенных для построения УУПЛ, таких как К589ИК01, К584ВУ1, К588ВУ2, К1800ВУ1 и др. можно встретить характерные элементы, рассмотренные выше.

Наиболее универсальными и обладающие широкими функциональными возможностями являются БИС для построения УУПЛ серии К1804. Ниже рассмотрены характерные БИС этого семейства.

Секции управления адресом микрокоманд серии К1804.

К БИС этой серии, предназначенных для реализации различных вариантов УУПУ (как микропрограммного, так и программного уровня), относятся микросхемы К1804ВУ1,2,3,4,5.

БИС . .ВУ5 предназначена для построения контроллера адреса (программный уровень) и будет рассмотрена позднее.

БИС . .ВУ1 и . .ВУ2 представляют собой 4-разрядные секции, обеспечивающие построение СФАМ произвольной разрядности (кратной четырем). Структуры. .ВУ1 и. .ВУ2 практически идентичны и управляются одинаково. БИС. .ВУ3 является вспомогательной для построения СФАМ на секциях. .ВУ1,2 (дешифратор инструкций, общий для всех секций).

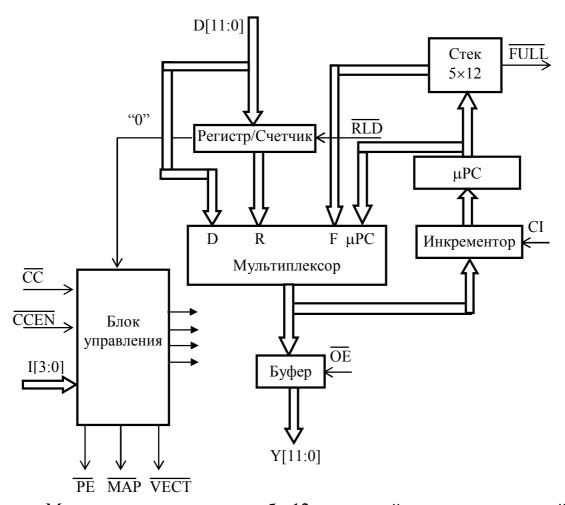

Наиболее популярна 12-разрядная несекционируемая схема управления последовательностью микрокоманд К1804ВУ4 (Рис.2.18), архитектура которой практически повторяет архитектуру секций. .ВУ1,2.

Рис.2.18. БИС К1804ВУ4

Микросхема включает в себя 12-разрядный микропрограммный счетчик mPC (счетчик адреса МК) с инкрементором, 5-уровневый стек, 12-разрядный регистр/счетчик Rg/C с детектором нуля, 12-разрядный мультиплексор  $4\times1$  выходной буфер с тремя состояниями и блок управления.

1.1.1.1.1.1. - вход непосредственного адреса;

**I[3:0]** - вход кода инструкции; СС\ - вход кода условия;

**ССЕN**\ - вход разрешения проверки условия;